Description

100BASE-T1 Automotive Ethernet Protocol Analyzer is the Protocol Analyzer with multiple features to capture and debug communication between host and design under test. Automotive Ethernet interface scales up to address current and future needs of in-vehicle bus speed requirements. The need for higher-speed in-vehicle buses is increasing to support feature-rich ADAS and connected vehicle needs. Two-wire full-duplex 100BASE-T1 PAM 3 signalling is the choice of interface bus to address these needs

Prodigy Technovations 100BASE-T1 Automotive Ethernet Protocol Analyzer provides an industry-first solution for the non-intrusively passive tap of the 100BASE-T1 bus at the physical layer and ensures no latency and accurate capturing of protocol data. Powerful basic and multi-level layer 2 to layer 7 protocol trigger capabilities enables the design engineer to capture protocol activity at a specific event. PGY-100BASE-T1-PA supports continuous streaming of captured protocol data to host computer SSD/HDD enabling long-duration capture.

Features 100BASE-T1 Protocol Analyzer

- Protocol decode and Analysis of 100BASE-T1 Bus.

- Passive tapping allows a non-intrusive method of monitoring the 100BASE-T1 Bus.

- Powerful multi-layer protocol layer trigger capabilities enable capturing data at specific events.

- Decoding of TC10 Sleep and Wakeup events of master and slave.

- Continuous streaming of protocol activity SSD/HDD enables long-duration capture of protocol data.

- Simultaneously monitoring of 100BASE-T1 and MDIO/MDC protocol activity.

- Live protocol decode capabilities allow you to view the protocol information while the test case actively running in DUT.

- The analytics feature provides statistical information on protocol packets.

- FCS error report helps in monitoring the protocol errors.

- The simplified Protocol Listing view with search and filter capabilities is easy to use.

- Software and firmware are fields upgradable

- Report generation.

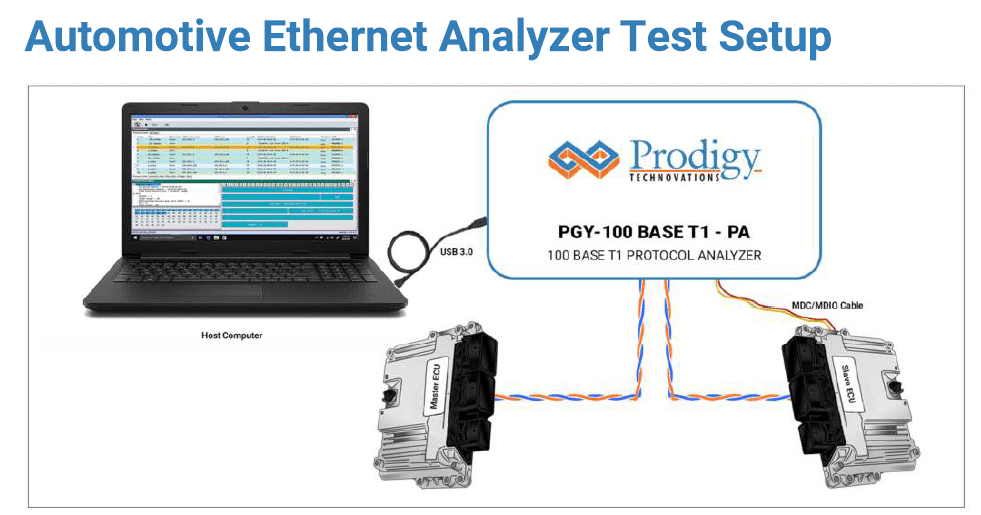

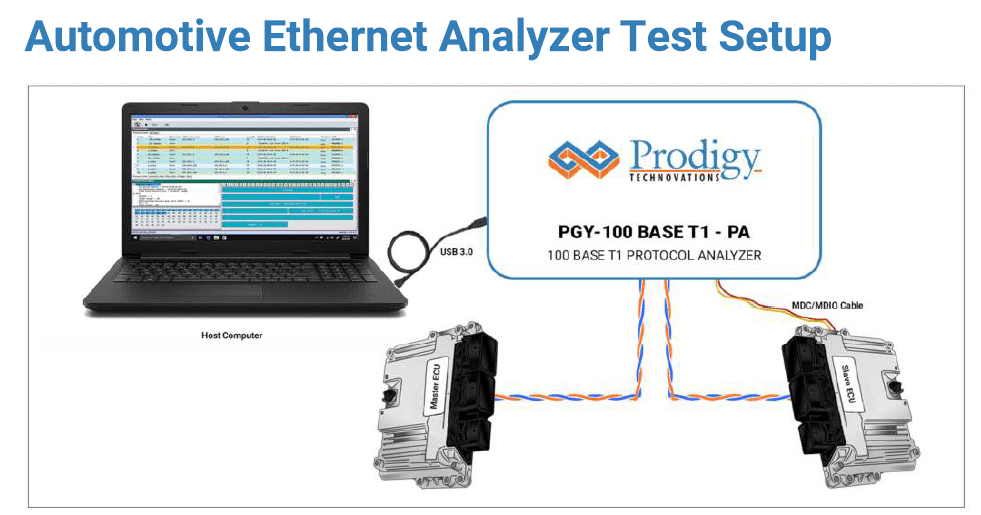

Automotive Ethernet Analyzer Test Setup

PGY-100BASE-T1-PA sniffs the automotive Ethernet bus and monitors the protocol activity between the Master and Slave ECU. Simultaneously monitoring MDIO and MDC lines and correlating with 100BASE-T1 protocol activity helps easy debug the design problems. The Automotive Ethernet Analyzer unit will extract bit values from full-duplex PAM3 signal using Prodigy’s patent-pending solution. The host computer manages the operation of the analyzer unit, and stores and analyzes the acquired data. Passive tapping of the 100BASE-T1 bus ensures the least latency in acquiring the data making this solution an industry-first Passive TAP patent-pending solution.

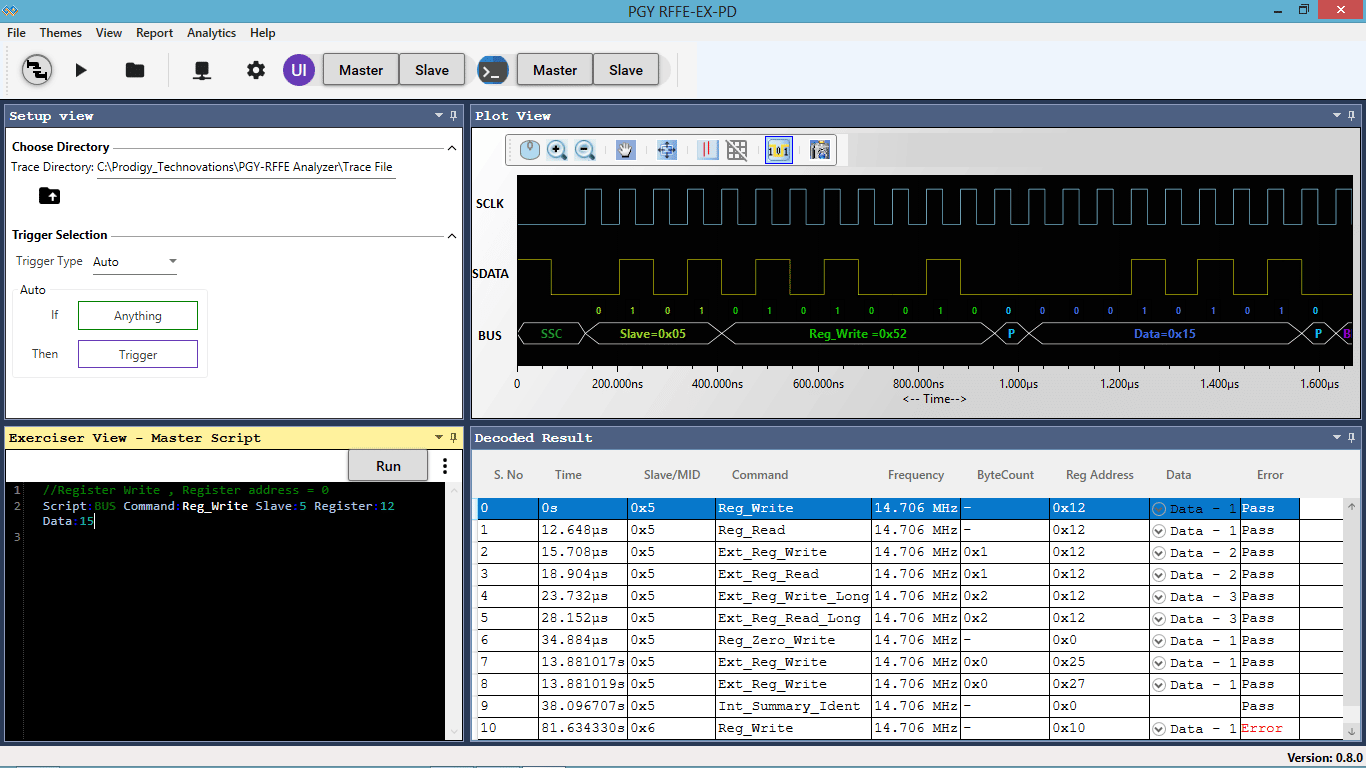

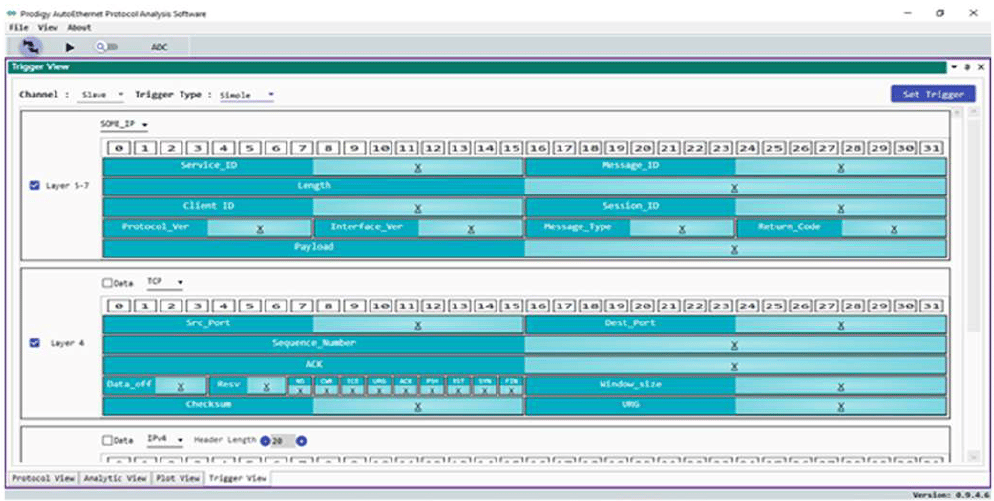

Powerful Trigger capabilities

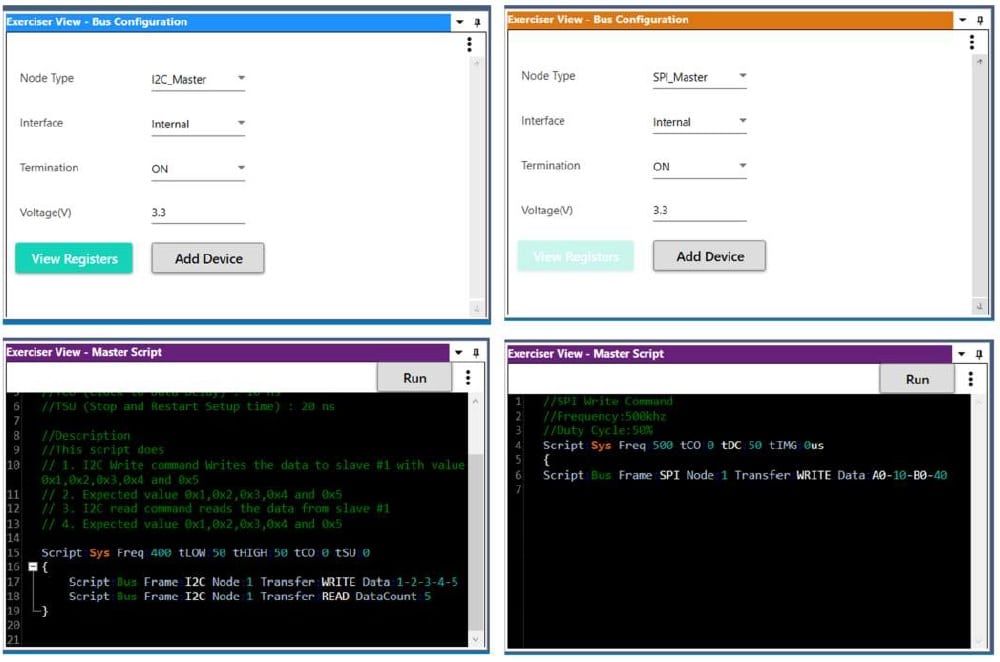

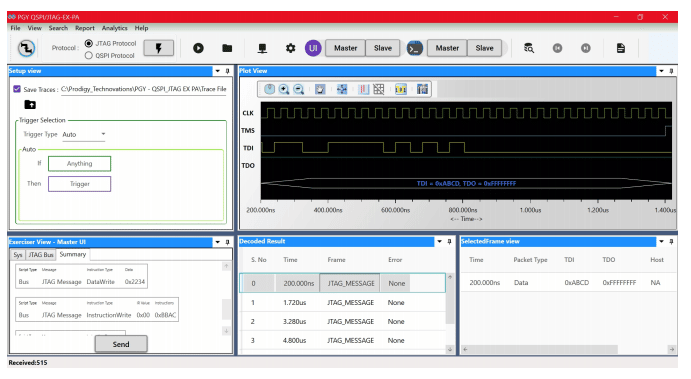

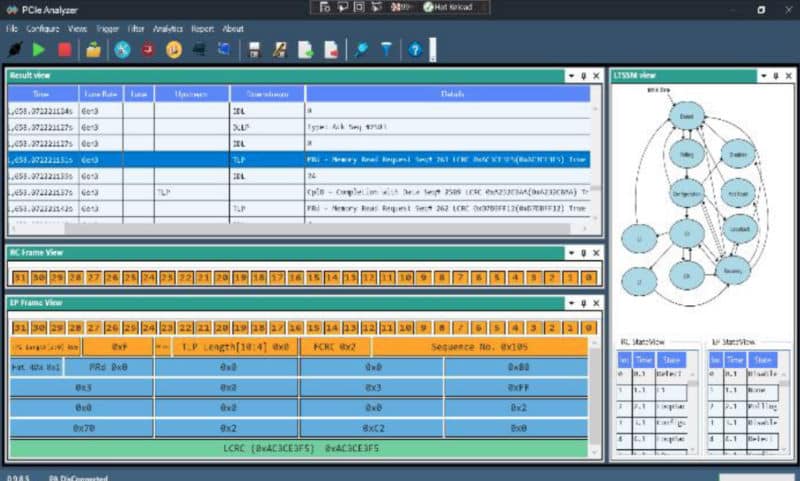

PGY-100BASE-T1-PA supports the industry’s best protocol layer trigger capabilities. Users can define trigger conditions from Layer 2 to layer 7. Advanced multi-layer trigger featured with If-then-else if allows the design engineer to monitor more than one trigger condition at the same time.

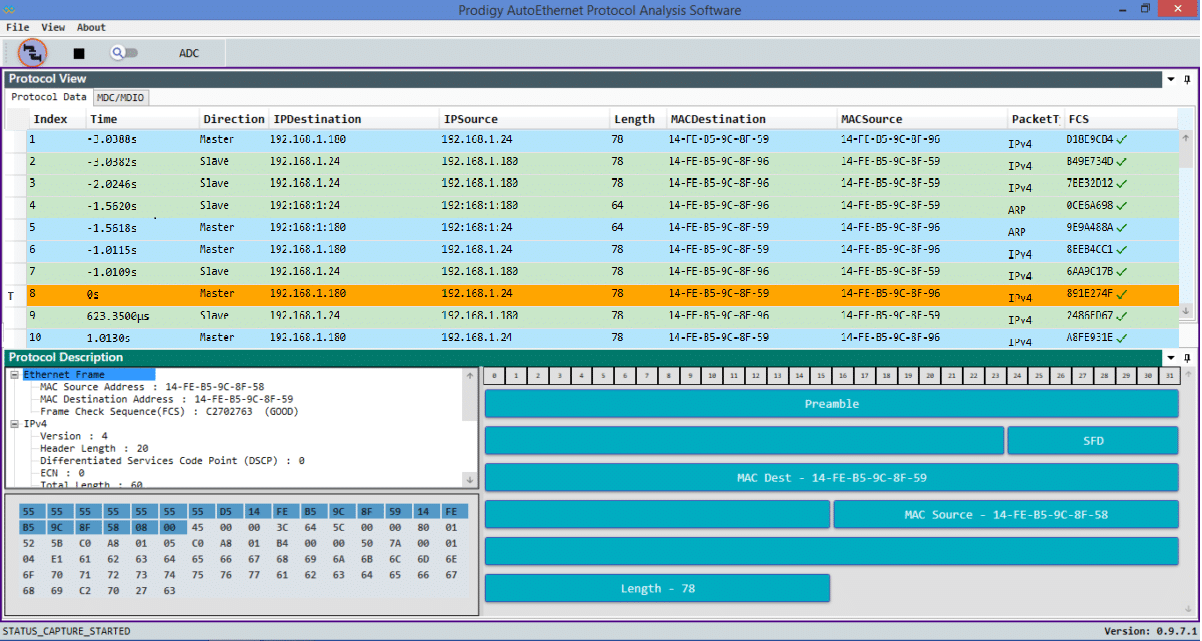

Protocol Analysis

Ethernet is one of the oldest protocols widely used protocol for many applications. Design engineers are used to viewing and analyzing the protocol data in a specific format. PGY-100BASE-T1-PA Protocol Analyzer software maintains the traditional views and provides advanced analysis capabilities. Live decoding capability provides decoding with any FCS error packets.

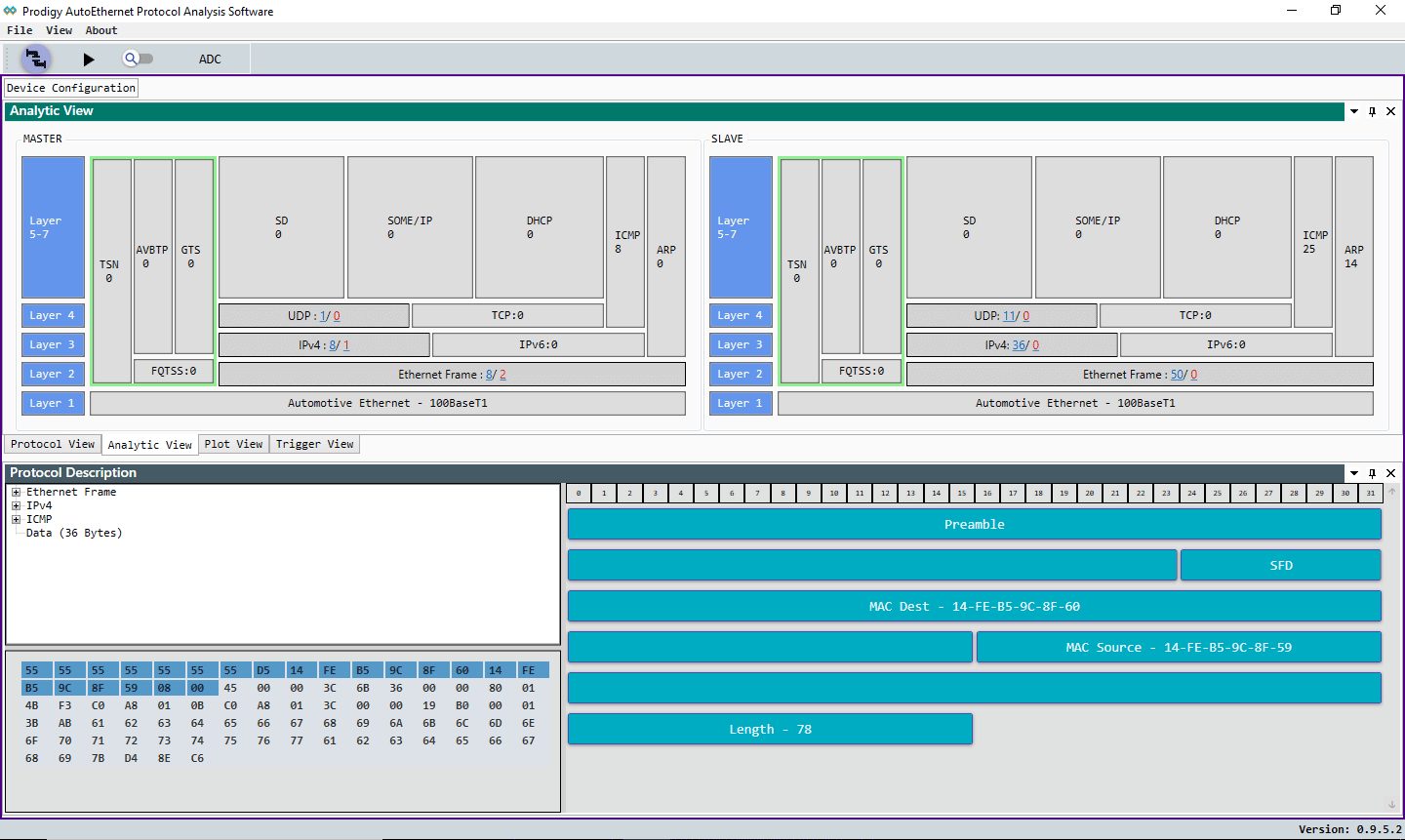

Setup Ansicht

Analyzing Protocol data to identify the design issues is a challenging task in millions of protocol packets. PGY-100BASE-T1-PA provides statistical information about each layer packet count and error packets. This simplifies the process of isolating the errors to specific protocol packets or protocol layers. Powerful expression-based search capabilities quickly help in locating packets of interest in the acquired entire protocol data for further analysis.

Warranty

Hardware and software are covered by a one-year warranty. Probes are covered months warranty for all manufacturing defects

Technical Data

| Specification | |

|---|---|

| Ports input | Four 100Base-T1 Ports Upgrade Two additional 100Base-T1 Port MDIO/MDC Port Two CAN Ports |

| Protocol Analysis | Layer 2 to Layer 7 Automotive Ethernet protocol Analysis MDIO/MDC Protocol Decode Upgradable to CAN Protocol Analysis |

| Protocol Views | Protocol Listing of Layer 2 Decoding of Protocol layer Packet view Tree view Line training view Analytics |

| Event Monitoring | FCS errors |

| Search and Filter | Boolean expression based search and filter capabilities |

| Capabilities Export of Results | CSV or TXT report generation |

| Host Computer System requirements | Windows® 7/8.0/8.1/10 64bit operating system. It requires RAM of 16GB but the product would give a faster response for a 32GB. The maximum storage capacity of 1GB should be available in the hard disk drive. Users can use more storage based on trace storage requirements. The Display resolution of the monitor is 1024x768 host Computer should support a USB 3.0 Interface. |

.jpg)

.jpg)

.jpg)

.jpg)