Description

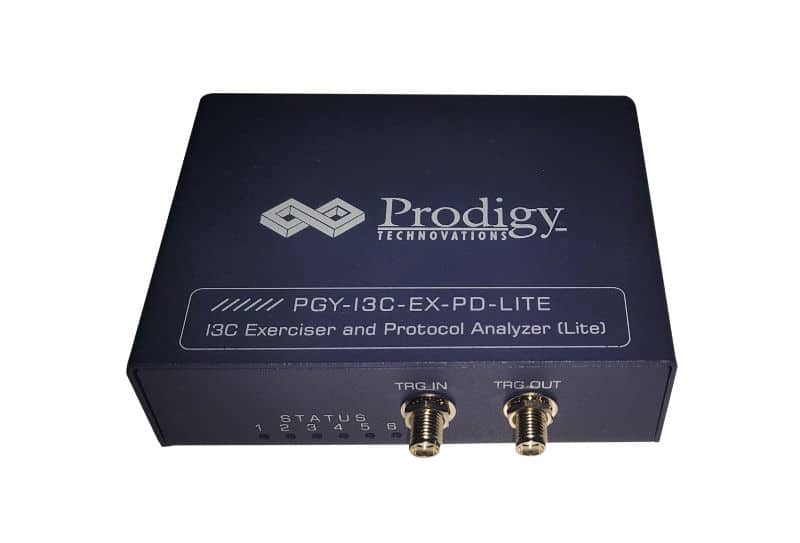

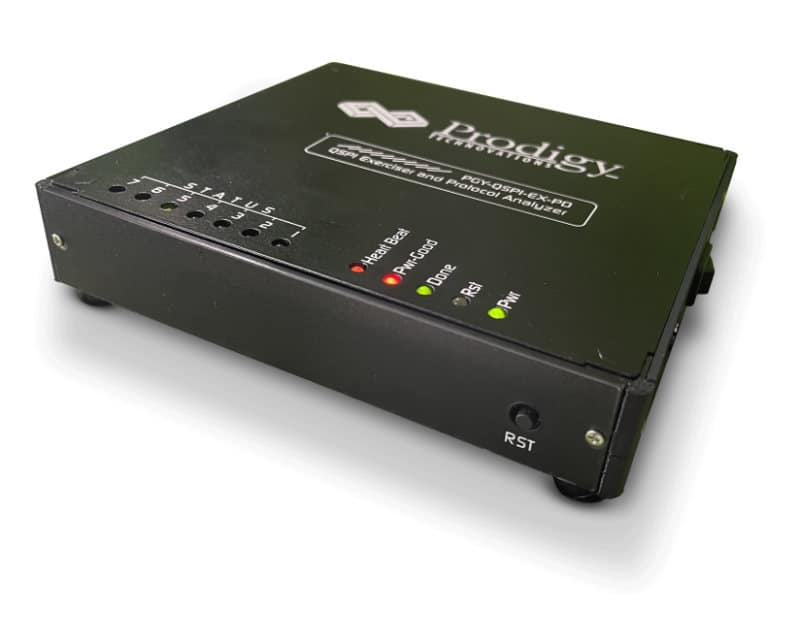

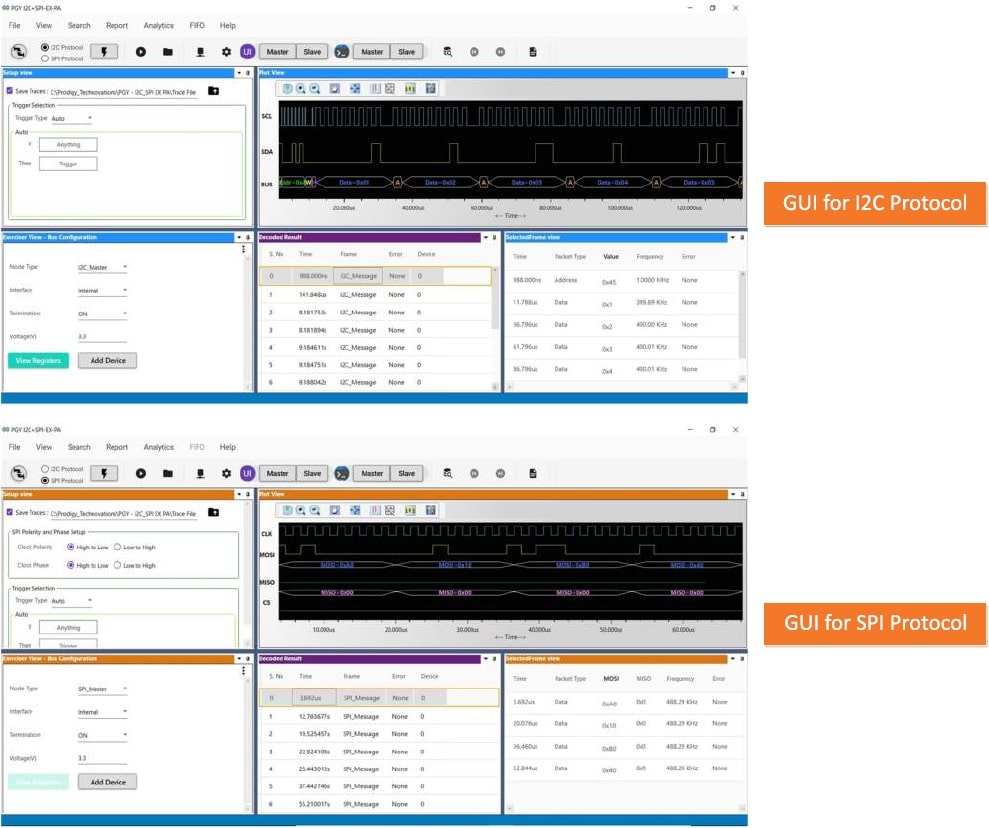

I2C Protocol Analyzer and SPI Protocol Analyzer(PGY-I2C/SPI-EX-PD) are the Protocol Analyzers with multiple features to capture and debug communication between host and design under test. PGY-I2C/SPI-EX-PD is the leading instrument that enables the design and test engineers to test the respective I2C or SPI designs for their specifications by configuring the PGY-I2C/SPI-EX-PD as Master/Slave, generating I2C/SPI traffic and decoding the I2C/SPI protocol decode packets

I2C is a two-wire interface to connect low-speed devices like microcontrollers, EEPROMs, A/D & D/A converters, I/O interfaces, and other small peripherals in embedded systems. The I2C bus is used by many ICs and is simple to implement. Any microcontroller can communicate with I2C buses. I2C buses can communicate on slow devices and can also use high-speed modes to transfer large amounts of data.

SPI is one of the widely used interfaces between micro-controller and peripheral ICs such as sensors, ADCs, DACs, shift registers, SRAM, and others. SPI is a synchronous, full-duplex master-slave-based interface. Both master and slave can transmit data at the same time. The SPI interface can be a 3 wire or 4-wire.

Features I2C/SPI Protocol Analyzer and Exerciser

- Supports I2C Specifications

- Supports SPI Specifications

- Ability to configure it as Master/Slave

- Generate different I2C/SPI Packets

- Variable data speeds

- Generate I2C/SPI traffic and protocol decode of the bus

- A timing diagram of the protocol decoded bus

- Listing view of protocol activity

- Ability to write exerciser script to combine multiple frame generation at different data speeds

- USB 2/3 host computer interface

- Continuous streaming of protocol activity to host system HDD/SSD

- API support for automation in python or C#

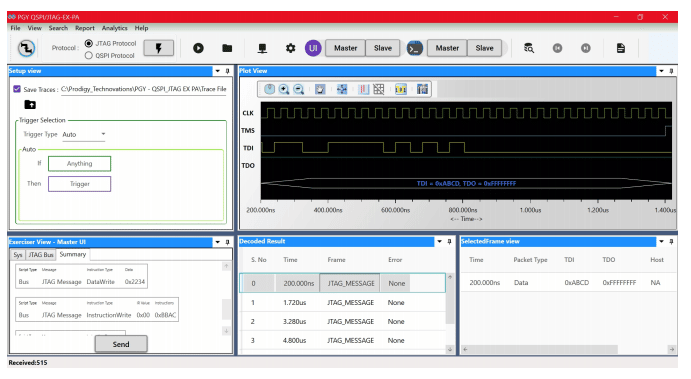

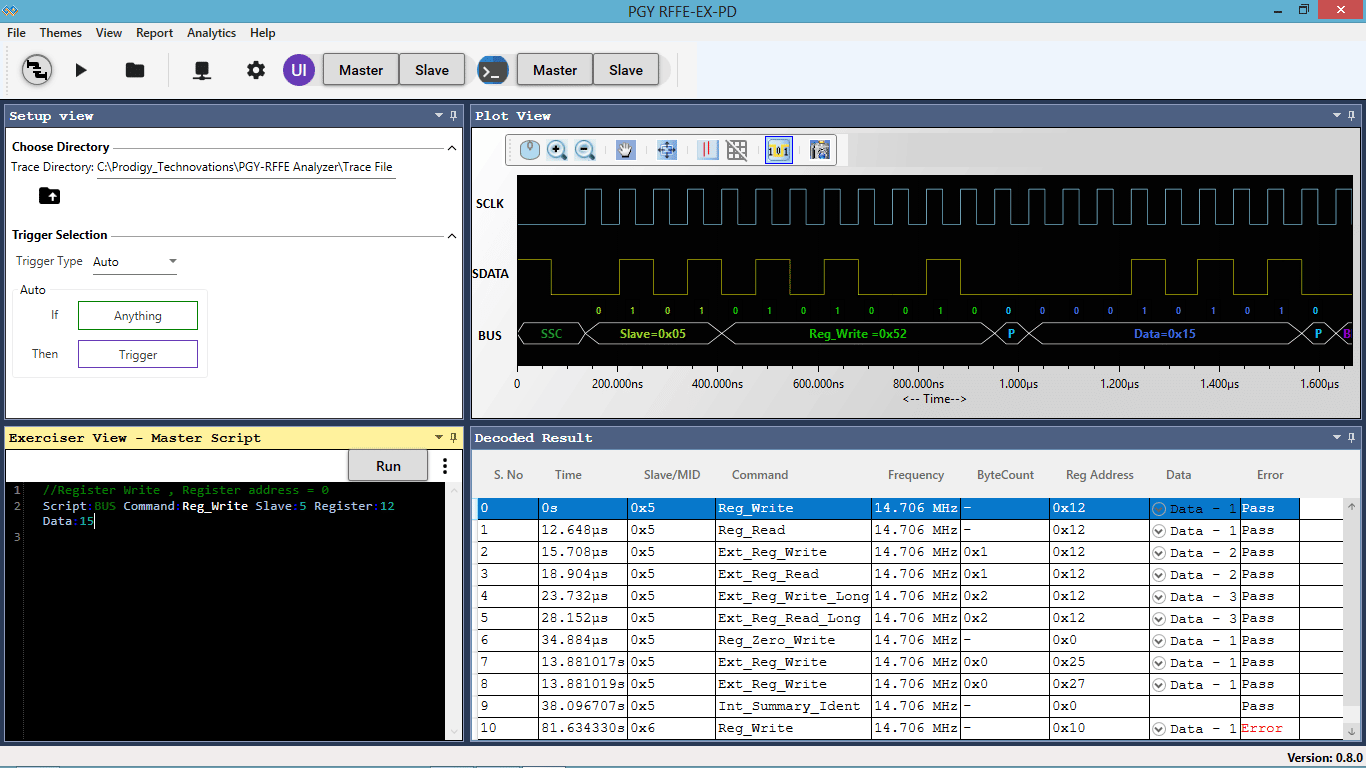

Comprehensive Protocol Analysis using Multi-View

Multidomain View provides the complete view of I2C or SPI Protocol activity in a single GUI. Users can easily set up the analyzer to passively monitor or use the exerciser to generate I2C or SPI traffic using a GUI or script. Users can set different trigger conditions from the setup menu to capture Protocol activity at a specific event and decode the transition between Master and Slave. The decoded results can be viewed in the timing diagram and Protocol listing window with autocorrelation. This comprehensive view of information makes it the industry best, offering an easy-to-use solution to debug the I2C or SPI protocol activity. Continuous streaming protocol activity to host system HDD/SSD ensures seamless roll mode operation without the need to recapture data when DUT/s are set to different states thereby saving test times.

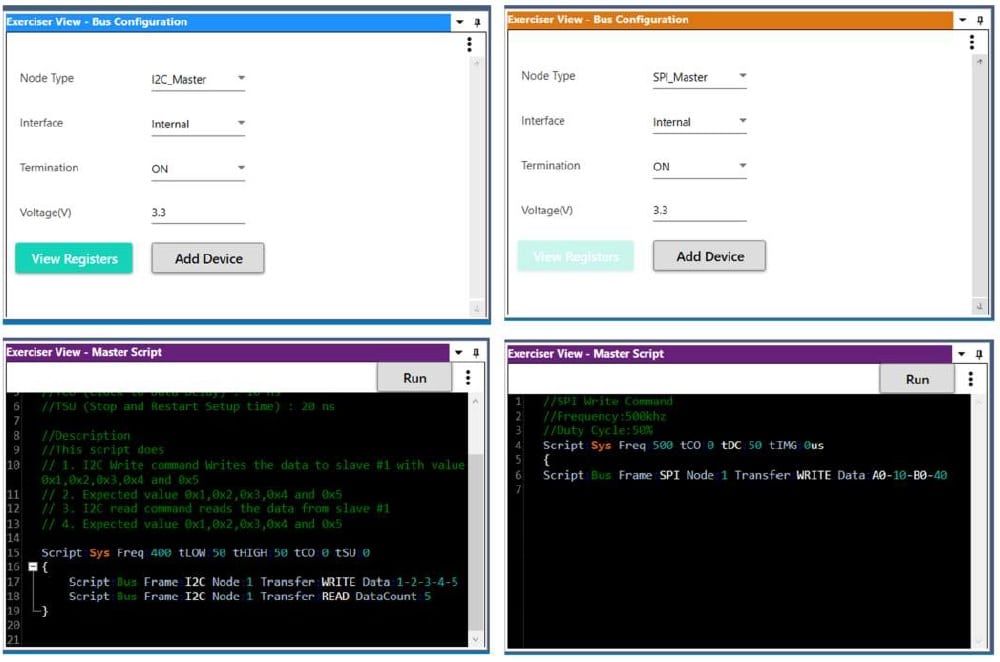

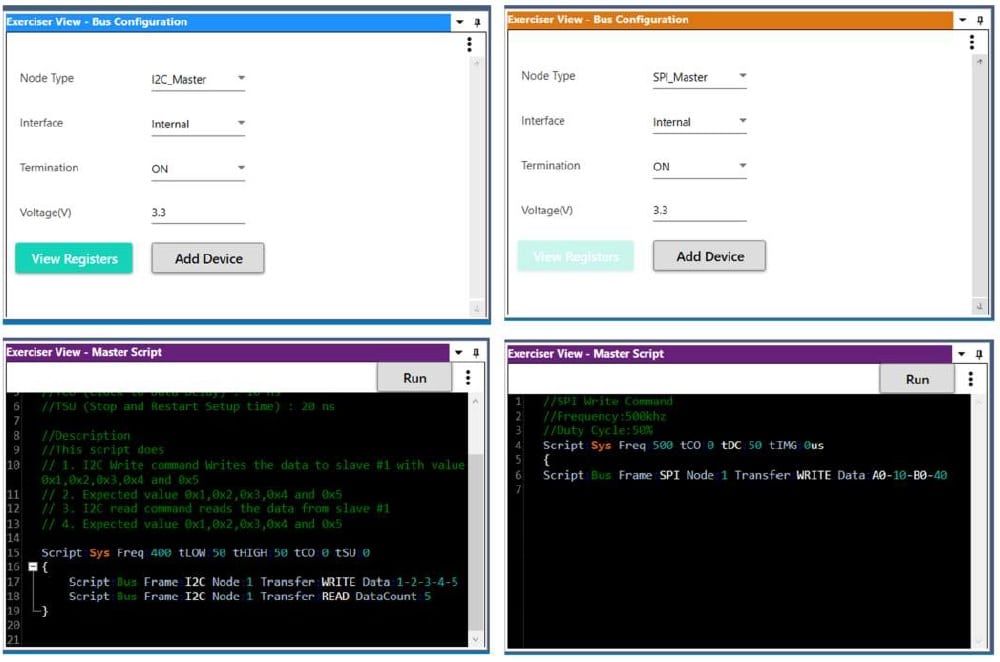

Exerciser

PGY- I2C/SPI -EX-PD supports I2C or SPI traffic generation using GUI and Script. Users can generate traffic using the GUI to test the DUT. Script-based GUI provides flexibility to emulate the complete expected traffic in real-time.

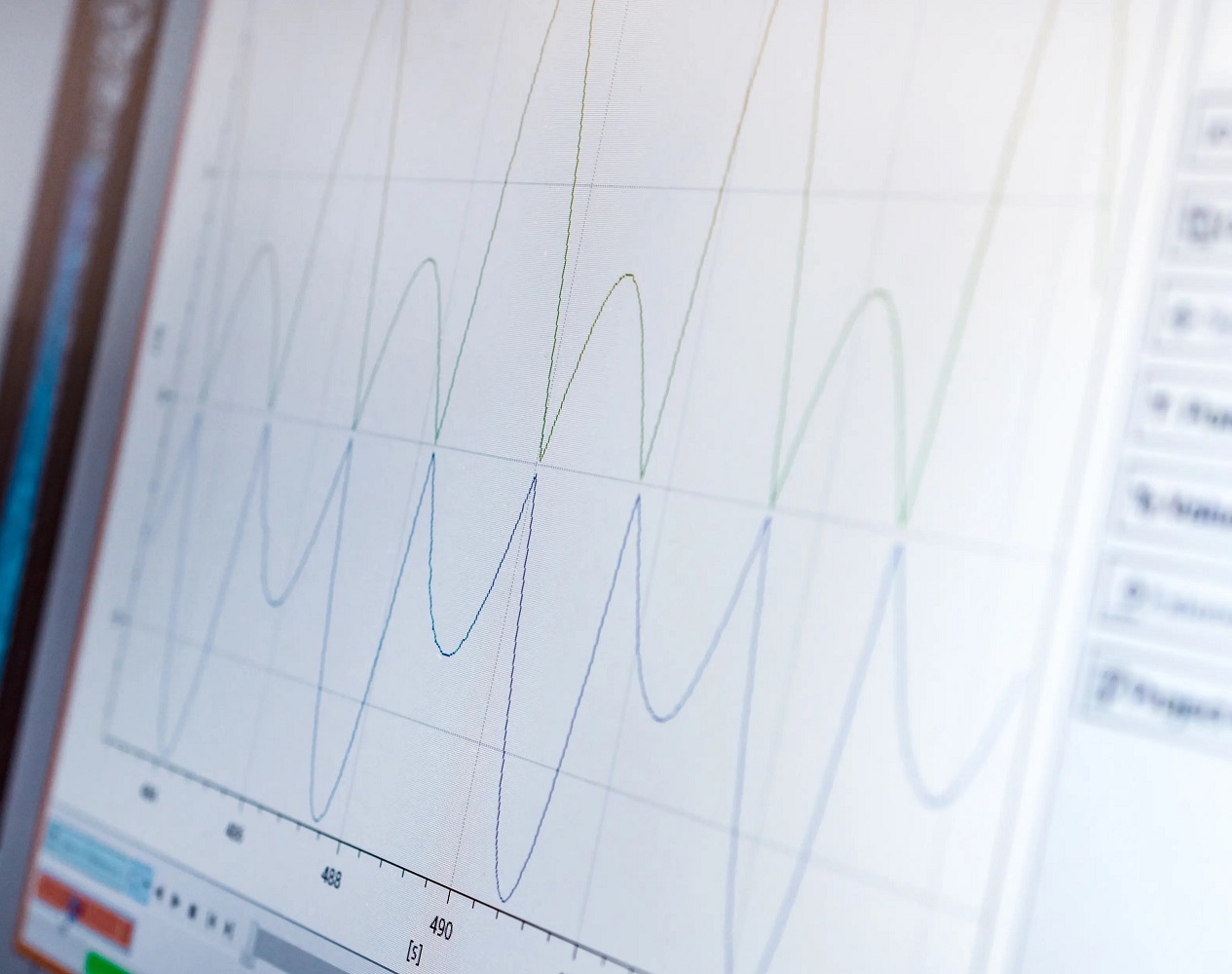

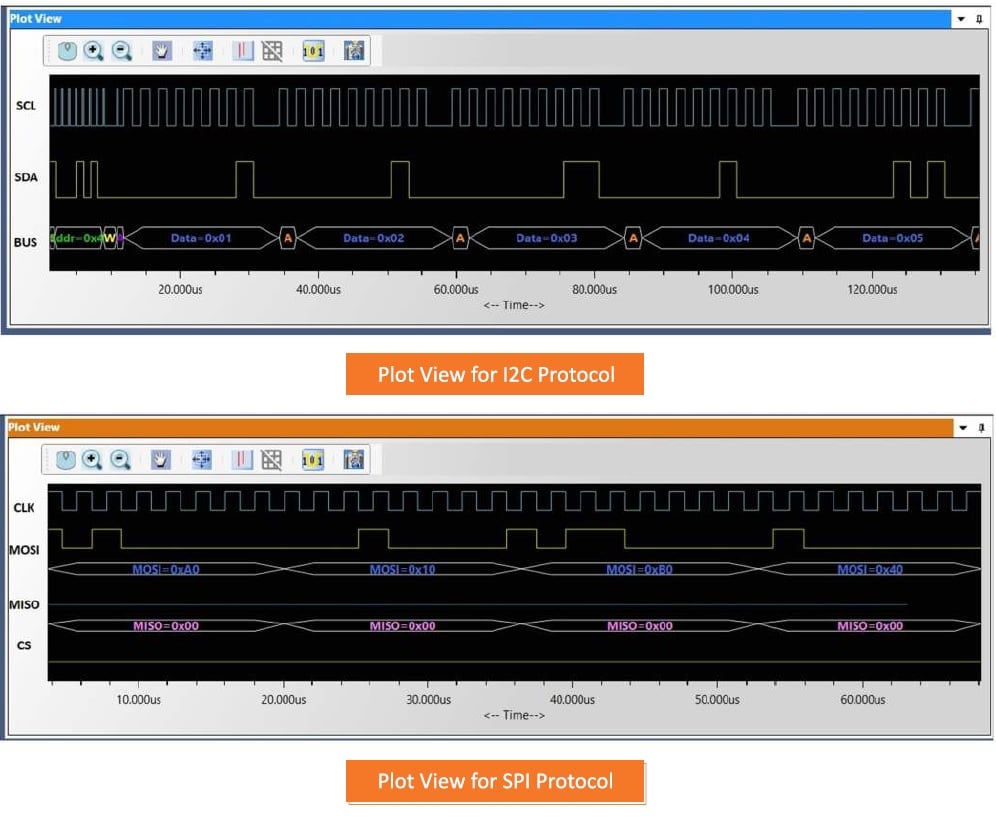

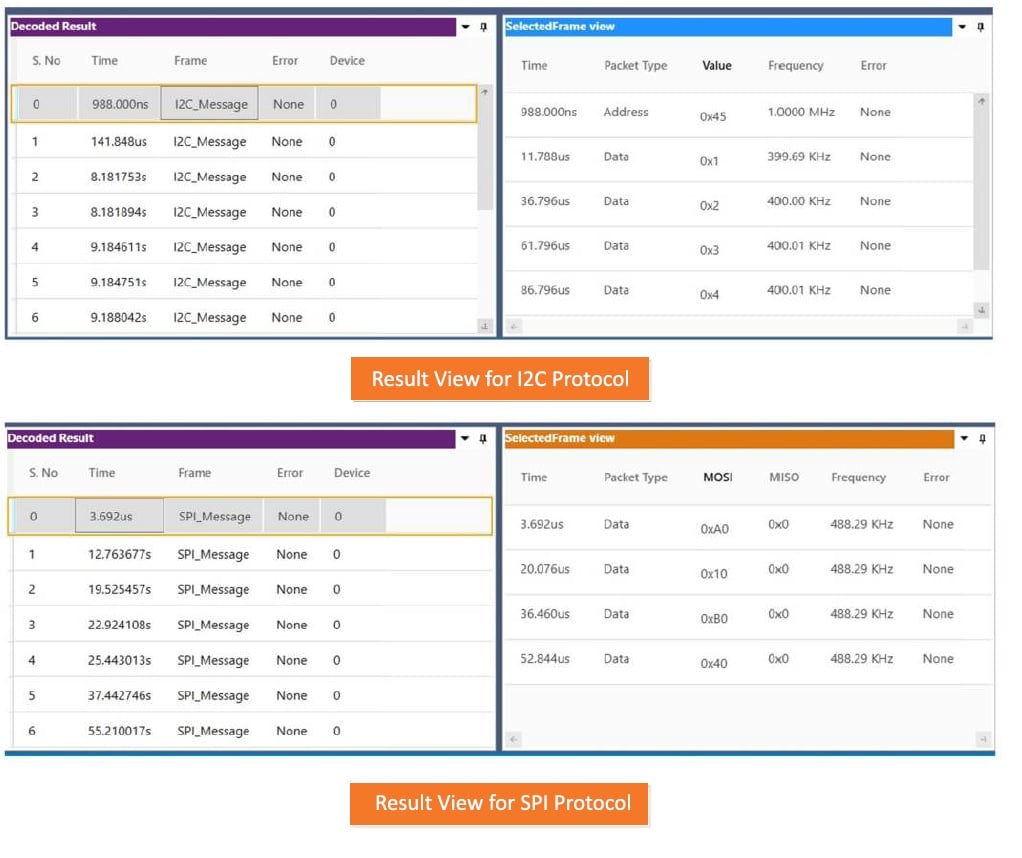

Timing Diagram and Protocol Listing View

The timing view provides the plot of the Clock and data signals with a bus diagram. Overlaying of Protocol bits on the digital timing waveform will help easy debugging of Protocol decoded data. Cursor and Zoom features will make it convenient to analyze Protocol in the timing diagram for any timing errors.

The protocol window provides the decoded packet information in each state and all packet details. The selected frame in the Protocol listing window will be autocorrelated in the timing view to view the timing information of the packet.

Powerful Trigger Capabilities

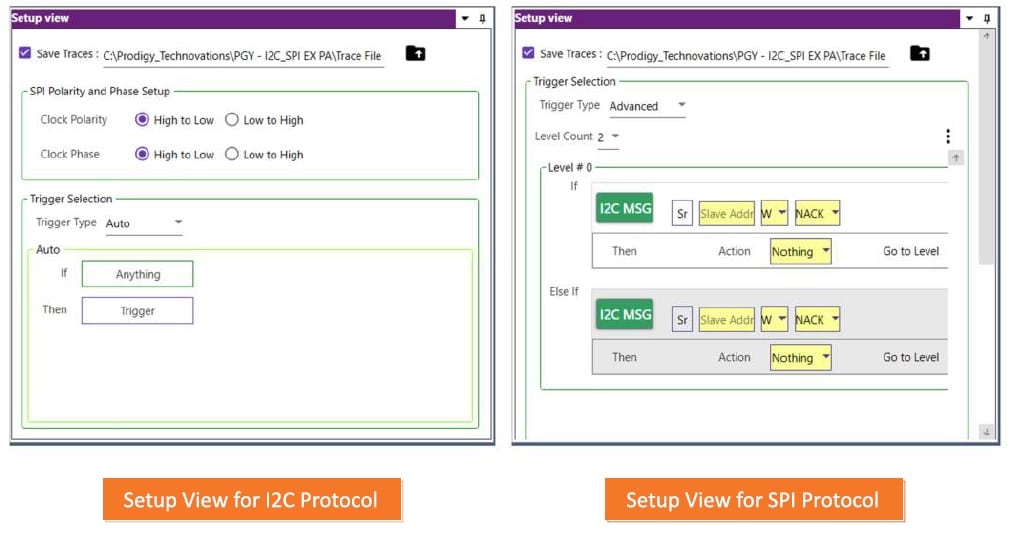

PGY-I2C/SPI-EX-PD supports simple trigger capabilities. The analyzer can trigger on any of the Protocol packets. Advanced Trigger provides the flexibility to monitor Multiple trigger conditions and can set multiple state trigger machines. Users can initiate a timer and trigger onset timer values.

Warranty

Hardware and software are covered by a one-year warranty. Probes are covered by a three-month warranty for all manufacturing defects

Technical Data

| Specification |  |

|---|---|

| Interfaces supported | I2C or SPI |

| Configurable | 1 I2C Master + 3 I2C Slaves or 1 SPI Master + 1 SPI Slave |

| I2C/SPI Traffic Generation | Custom I2C/SPI traffic generation |

| Clock Frequency | Up to 3.4 MHz for I2C. Variable up to 32 MHz, Fixed Up to 50MHz for SPI |

| FIFO Capacity | I2C: Yes, 8K read and 8K write on master & 1K on Slave |

| Voltage Drive Level | 1V to 3.3V for I2C. 1V to 3.3V for SPI. Variable in steps of 100mV |

| Command sequence Support | All command sequence is supported |

| Clock Duty Cycle variation | User Devine for I2C. 25%, 50% or 75% for SPI |

| Clock & Data Delay | User defined for I2C. User defined for SPI. |

| Delay between two messages | Customisable Delay |

| API Support | I2C: Yes SPI: Yes |

| Support | I2C and SPI Protocol |

| Protocol Views | Timing Diagram View Protocol Listing View Bus Diagram to display Protocol packets with timing diagram plot |

| Protocol Trigger | I2C Trigger Capabilities: Auto Trigger, Message Trigger - Trigger Slave Address for write or read command on NACK and Trigger Slave Address and Data for Write or Read command on ACK. Advanced multi-level multiple condition trigger |

| Capture Duration | Continuous streaming Protocol Data |

| Report Generation | CSV/PDF format |

| Host Connectivity | USB 3.0 /2.0 Interface |

| Dimension | 157mm x 90,2mm x 26,6mm |

| Net weight | 290 gms |

| Gross Weight | 1,05 Kg |