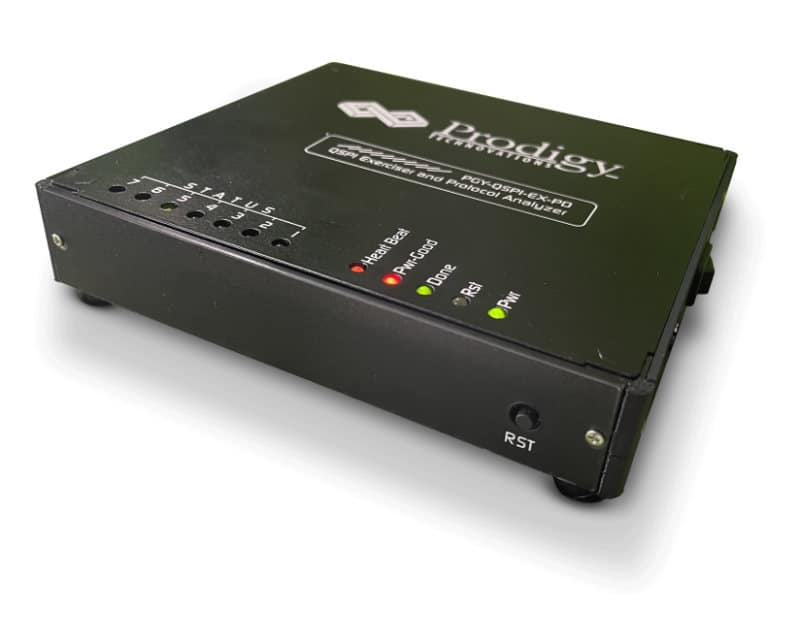

Protocol Analyzer & Logger

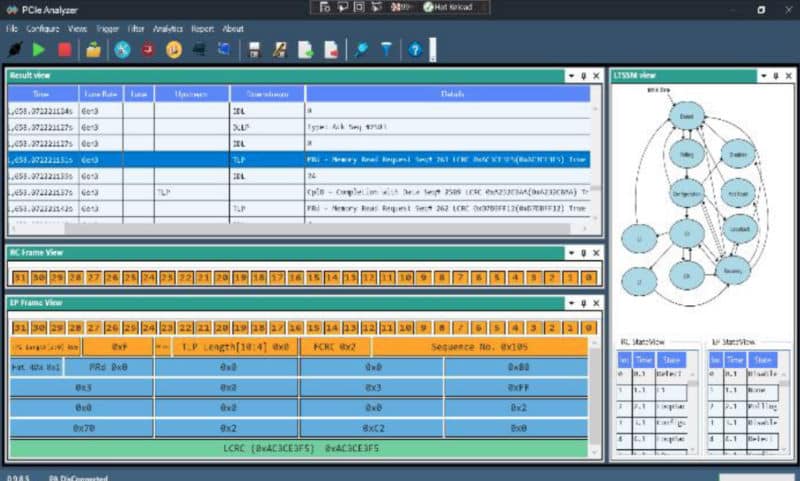

Compared to an oscilloscope, a protocol analyzer offers the advantage of being able to record large amounts of data in real time and to display the bit stream decoded in plain text such as hex. However, if the physical waveform is to be recorded and viewed, the use of a oscilloscope is recommended. We offer the widest range of protocol analysis solutions for monitoring data transmissions on various bus networks. Below are some of the supported protocols.

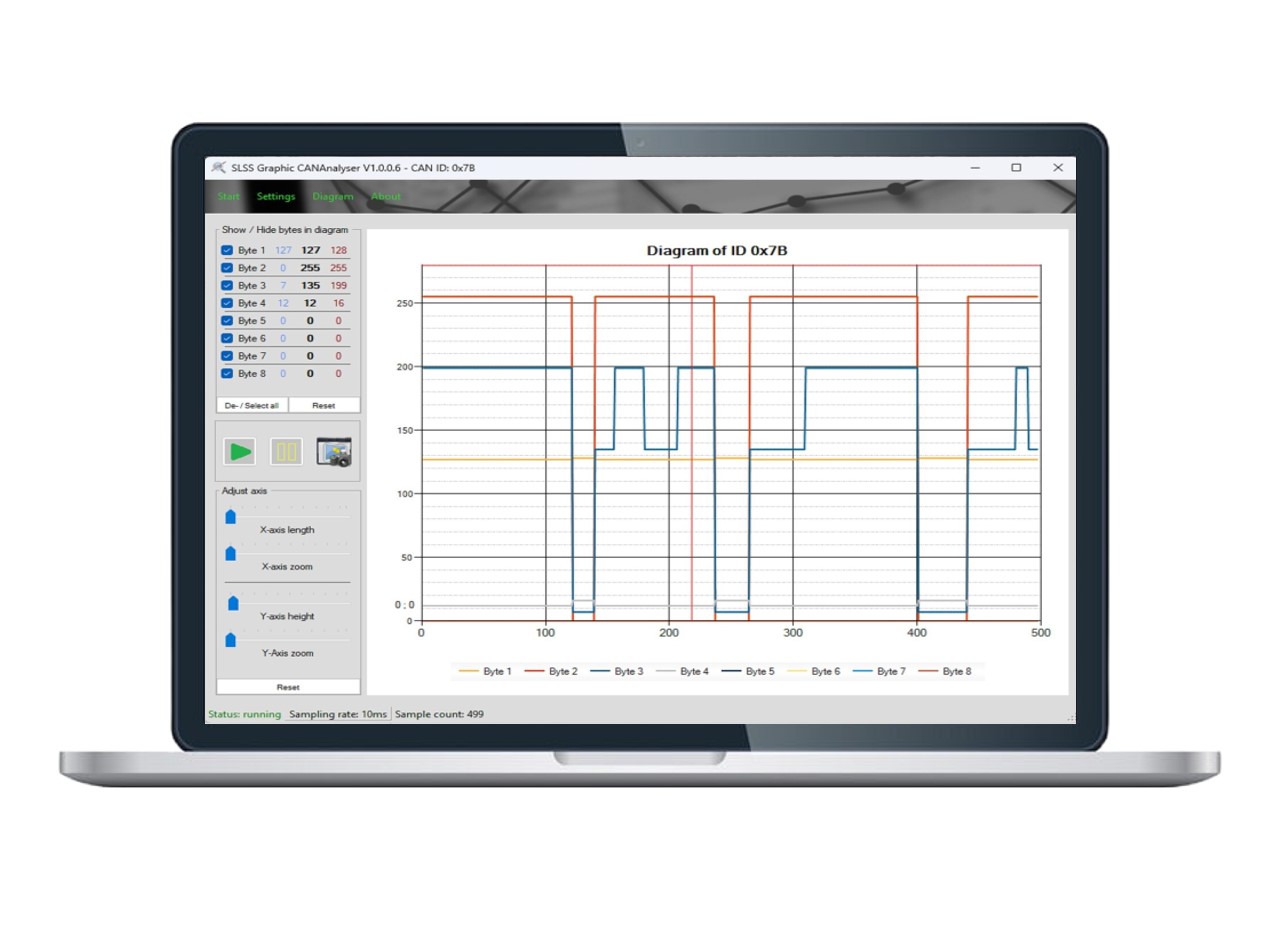

CAN

The Controller Area Network (CAN) bus was developed by Bosch in 1983 and presented in 1986 together with Intel. The goal when creating it was to reduce cable harnesses in order to save costs and weight and to enable faster communication between electronic components. At that time, the total length of all cables in vehicles without CAN could be up to 2 km. Today it is indispensable in the automotive sector and has become a common standard. Due to the many advantages with regard to conventional communication protocols, the CAN bus is also used in the fields of automation, building services, military or even in medical electronics.

When developing and debugging with the Controller Area Network Bus, it is often necessary to send test transmissions or to identify errors and their origin as quickly as possible in order to correct them as quickly as possible. A CAN bus adapter is often the best solution here to get full access to the CAN bus network and to carry out distortion-free monitoring.

eMMC

An eMMC (embedded Multi Media Card) is an energy and space-saving storage medium specified by JEDEC, based on the MMC standard, which was developed for use as internal data storage in mobile devices. In terms of performance, this memory is comparable to an SD card and is therefore installed in compact end devices. Since the eMMC is bootable, this storage medium is also suitable for operating systems such as Android, Chrome OS, iOS or Windows. The memory size ranged up to 256 GB in 2017. eMMC, especially in smartphones, are increasingly being replaced by UFS, which achieve significantly higher write and read speeds.

The Prodigy eMMC Protocol Analyzer is a multifunctional solution for capturing and debugging the communication between the host and the memory under test. It is the first eMMC protocol analyzer in the industry to support the 4.41, 4.5.1, 5.0 and 5.1 specifications.

eSPI

The Enhanced Serial Peripheral Interface (eSPI) developed by Intel was developed as a replacement for the LPC (Low Pin Count) bus. The advantages of the eSPI include the number of pins required, the higher data throughput, the lower working voltage (1.8V) and the shared use of SPI flash devices. These advantages enable a smaller process chain in chip manufacture. In addition, eSPI enables system designers to make early cost and performance assessments of their system. eSPI uses the physical interface designed for SPI, including the master-multi-slave topology.

Our eSPI protocol analysis solution enables you to monitor the communication between a master and multiple slaves on the data lines. The eSPI example data can be used to simulate an eSPI master.

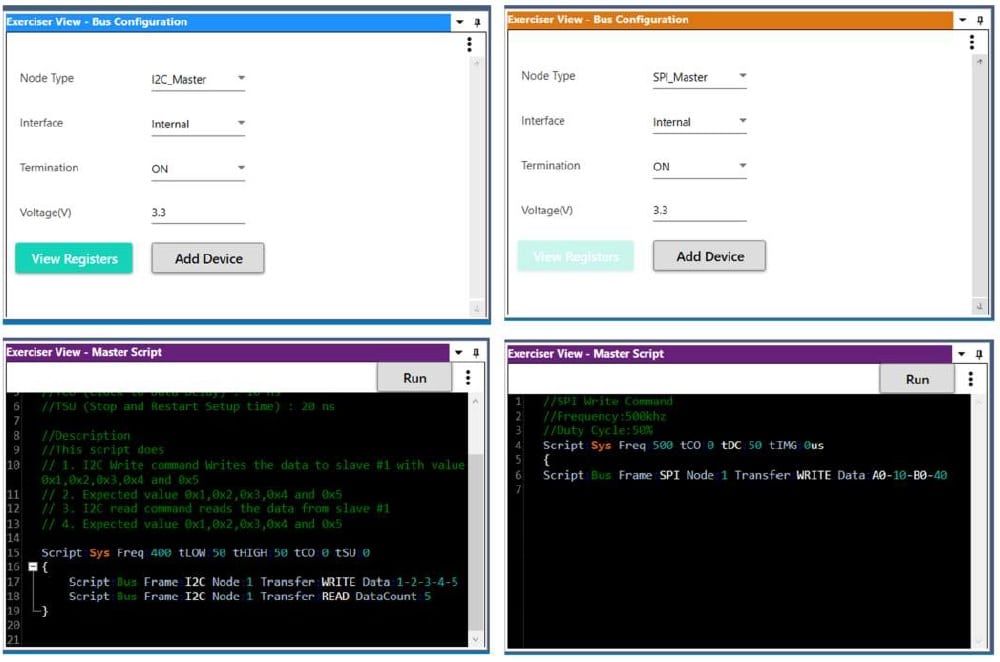

I2C

The Inter-Integrated Circuit (I2C / I2C) bus is a serial data bus developed by Philips Semiconductors. It is mainly used inside the device for communication between different circuit parts, e.g. B. between a controller and peripheral ICs.

With the Beagle I2C / SPI protocol analyzer, data traffic can be easily debugged and monitored using suitable protocol analysis software (data center).

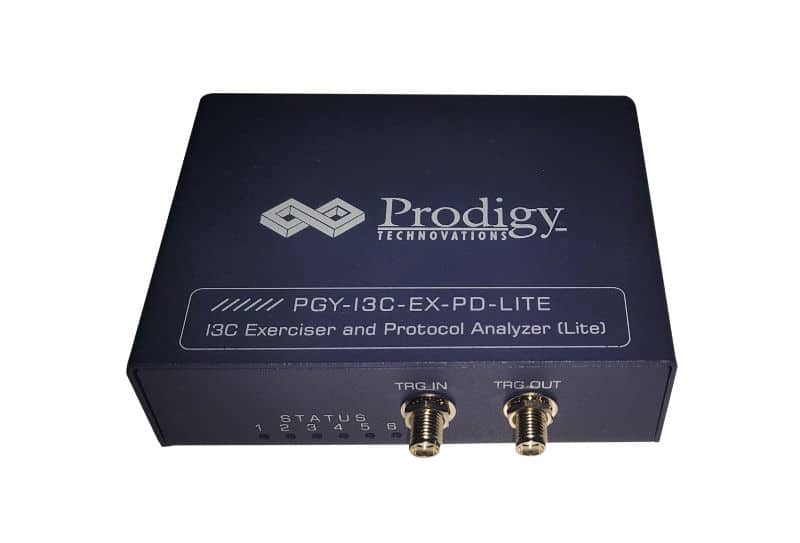

I3C

The PGY-I3C-EX-PD series is the world's leading solution for testing I3C designs. The devices of the PGY-I3C-EX-PD series can be configured as master or slave, generate the I3C data traffic with error injections and decode the packets of the I3C protocol.

The Prodigy I3C Analyzer and Exerciser series includes a Lite version and a Full version with full functionality and maximum hardware performance.

RFFE interface

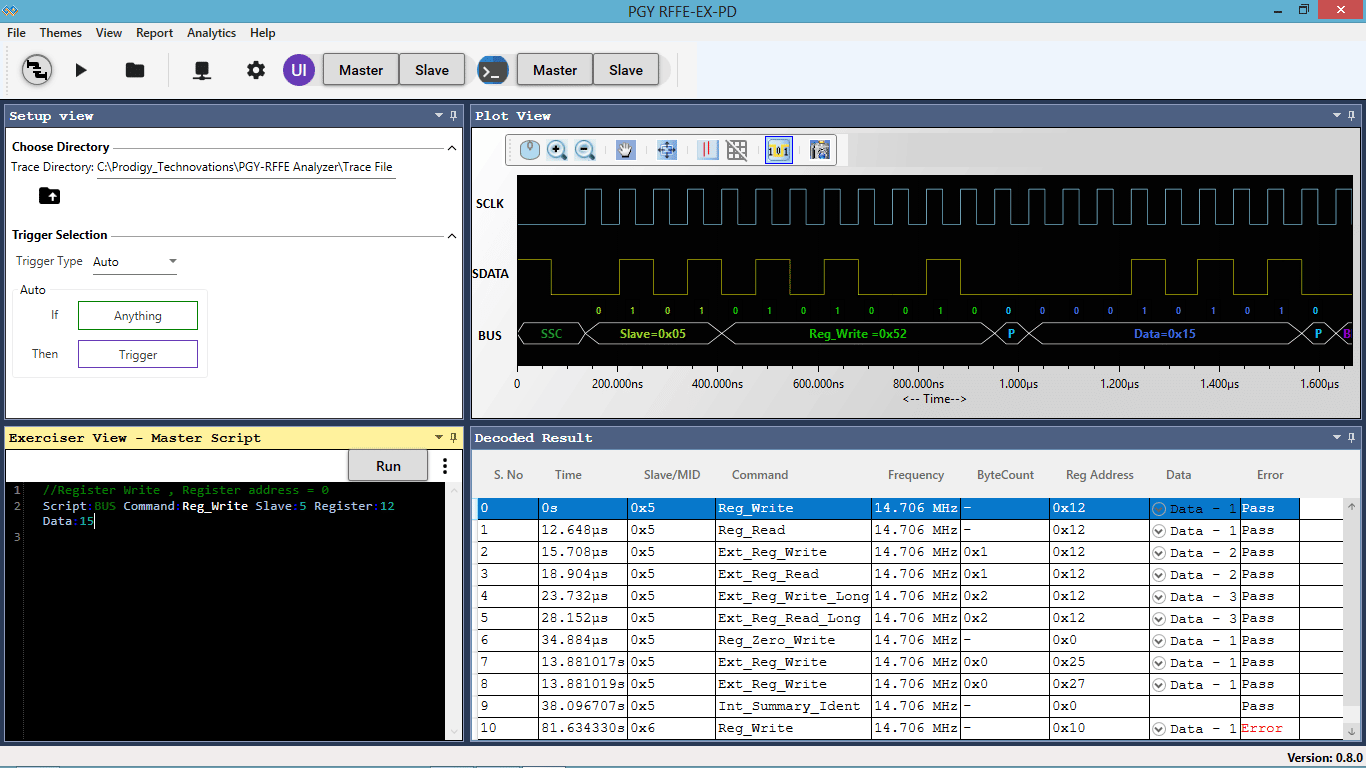

Originally released in July 2010Released MIPI RFFE SM , the MIPI RF Front-End Control Interface , is the world's de facto standardized interface for controlling radio frequency front-end (FE) subsystems. It provides fast, agile, semi-automated and comprehensive control of the complex RF subsystem environment that has stringent performance requirements and includes up to 19 components per bus instance (up to 15 slave devices and up to four master devices). Power supplies can include amplifiers, LNAs, antenna tuners, filters and switches.

Prodigy's RFFE Protocol Analyzer is the ideal tool for design and test engineers to test the RFFE interface against their specifications. The device can be configured both as a master and as a slave, in order to enable the generation of RFFE traffic with error injections, amplitude variation and decoding of the RFFE protocol packets in addition to the protocol analysis.

SD

Secure Digital , officially abbreviated as SD , is a proprietary non-volatile memory card format developed by the SD Card Association (SDA) for use in portable devices. The Secure Digital Input Output (SDIO) is an extension of the SD specification to cover I/O functions. SDIO cards are only fully functional in host devices that support their input/output capabilities (usually PDAs like the Palm Treo, but occasionally laptops or cell phones). These devices can use the SD slot to support GPS receivers, modems, barcode readers, FM radio tuners, TV tuners, RFID readers, digital cameras and interfaces Use Wi-Fi , Bluetooth , Ethernet and IrDA. Many other SDIO devices have been proposed, but it is now more common for I/O devices to connect via the USB interface. SDIO cards support most SD card storage commands. Prodigy Technovations protocol analyzers enable development and verification engineers to test and debug SD as well as SDIO by targeting Command, Response, Data or to Trigger CRC error.

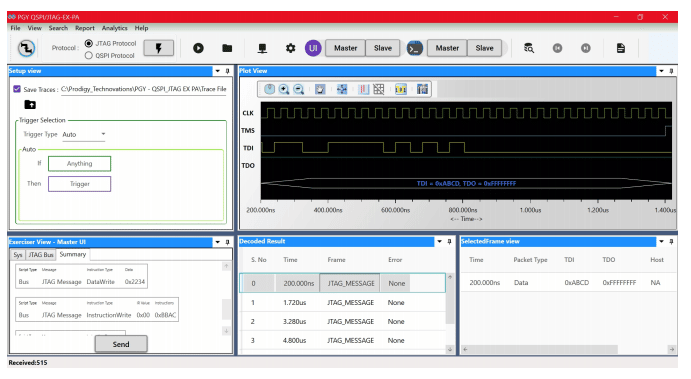

SPI

The Serial Peripheral Interface (SPI) is a bus system developed by Motorola (now NXP Semiconductors) in 1987 and represents a standard for a synchronous serial data bus (Synchronous Serial Port) with which digital circuits can be connected to each other according to the master-slave principle. The Beagle SPI Protocol Analyzer enables the entire bus data traffic to be monitored and can be operated intuitively with the appropriate analysis software (Data Center).

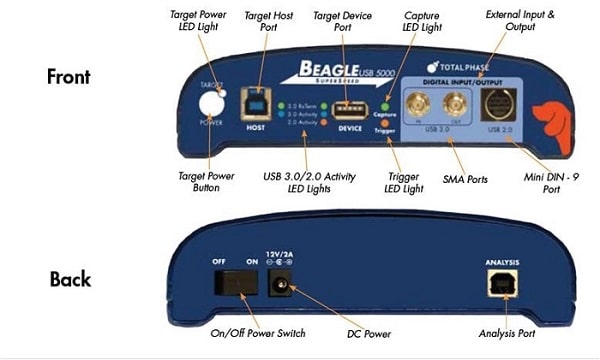

USB

USB was introduced in 1996 as USB 1.0 with a maximum data rate of 12 Mbit/s. In the year 2000, version USB 2.0 was specified, with 480 Mbit/s still the most common version today. With the USB 3.0 standard introduced in 2008, the maximum gross data transfer rate for SuperSpeed is 5 Gbit/s. Even with USB 1.0, it was possible to supply power to connected devices via the USB cable connections. Due to the greatly increased possible power consumption, verification of the embedded system is now necessary. Our solutions enable you to monitor the data traffic as well as the voltage and power supply on the USB bus.

UFS

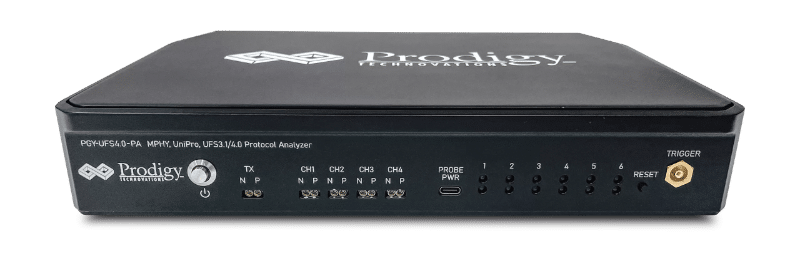

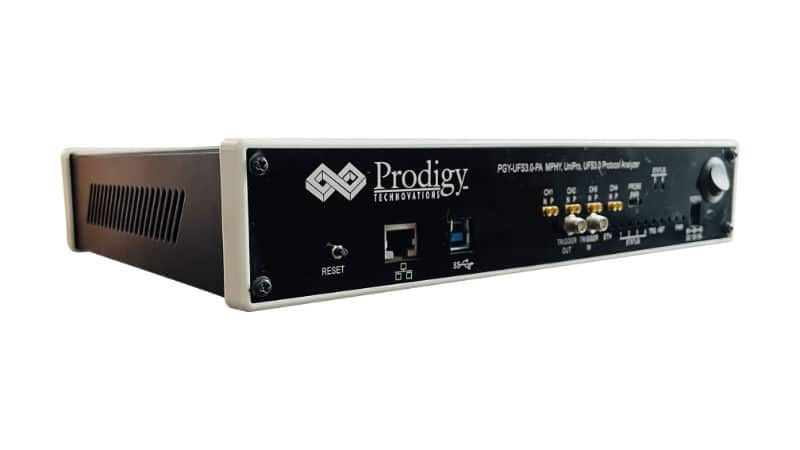

In 2011 the first standard version of UFS was released. There are now 6 different versions of UFS that achieve a maximum data transfer speed of up to 1450 MB/s, which is three times the data transfer speed of the fastest modern eMMC’s. With our solutions for UFS, in addition to the acquisition and debugging of MPHY, UniPRO and UFS, the immediate decoding of UFS layers, UniPRO layers and MPHY layers is possible.

Price on request

Price on request

Price on request

Price on request

Price on request

Price on request

Price on request

Price on request

Price on request

Price on request

Price on request

Price on request

Price on request

Price on request

Price on request

Price on request

Price on request