Description

UART Protocol Analyzer (PGY-UART-EX-PD) are the Protocol Analyzers with multiple features to capture and debug communication between host and design under test. PGY-UART-EX-PD is the leading instrument that enables the design and test engineers to test the respective UART designs for their specifications by configuring the PGY-UART-EX-PD as Master/Slave, generating UART traffic and decoding the UART protocol decode packets.

UART stands for Universal Asynchronous Receiver Transmitter. A UART’s main purpose is to transmit and receive serial data. PGY-UART-EX-PD is the leading instrument that enables the design and test engineers to test the UART designs for their specifications. Generating UART traffic with custom traffic capability and decoding UART Protocol packets.

Features PGY-UART-EX-PD UART Protokoll Exerciser and Analyzer

- Supports custom UART traffic generation

- Simultaneously generate UART traffic and Protocol decode of the bus

- Variable UART baud rates

- Continuous streaming of protocol data to the host computer to provide a large buffer

- A timing diagram of Protocol decoded bus

- Listing view of Protocol activity

- Error Analysis in Protocol Decode

- Ability to write exerciser script to combine multiple data frame generation at different data speeds

- USB 2.0/3.0 host computer interface

- API support for automation in Python or C++

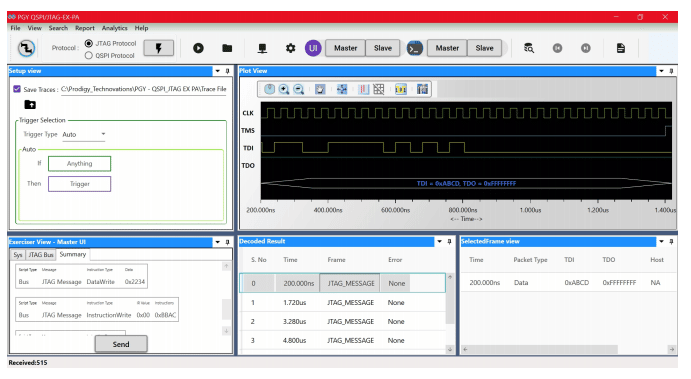

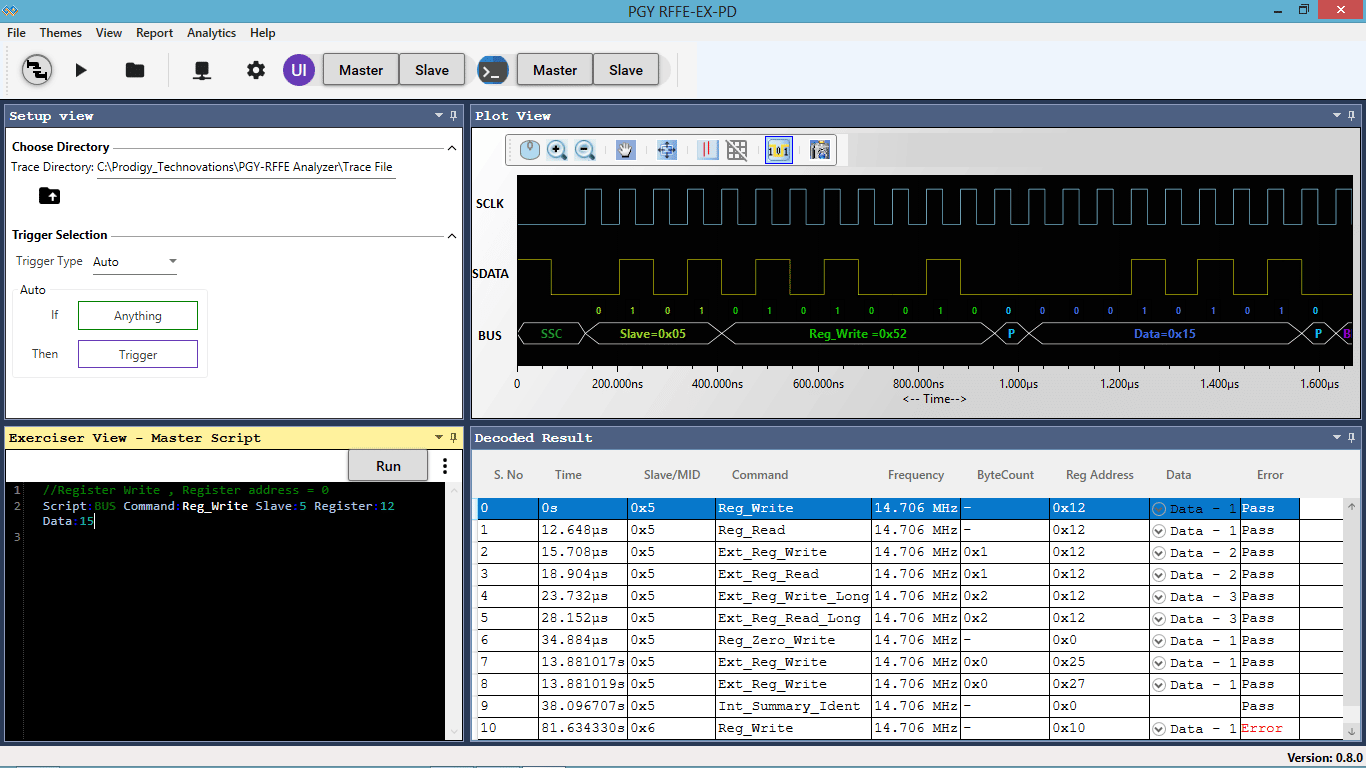

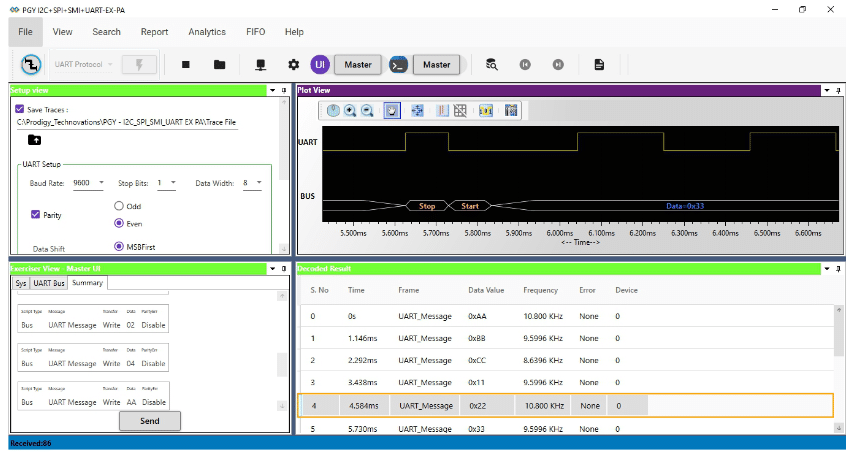

Multi-Domain View

Multi-domain View provides the complete view of UART Protocol activity in a single GUI. Users can easily set up the analyzer to generate UART traffic using a GUI or script. Users can capture Protocol activity at a specific event and decode the transition on the UART line. The decoded results can be viewed in the timing diagram and Protocol listing window with auto–correlation. This comprehensive view of information makes it the industry’s best, offering an easy-to-use solution to debug the UART protocol activity.

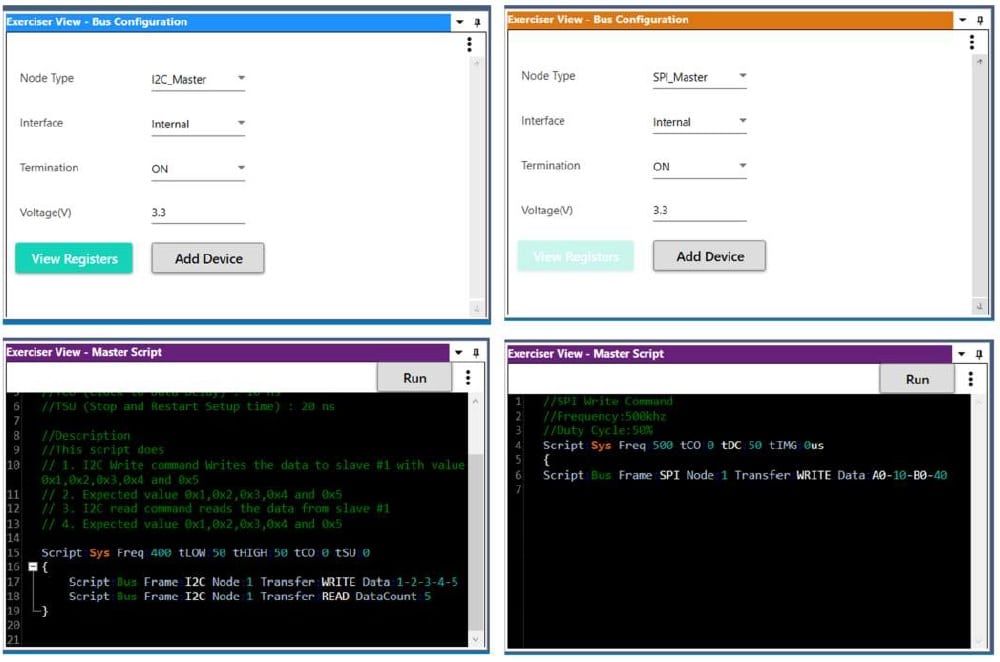

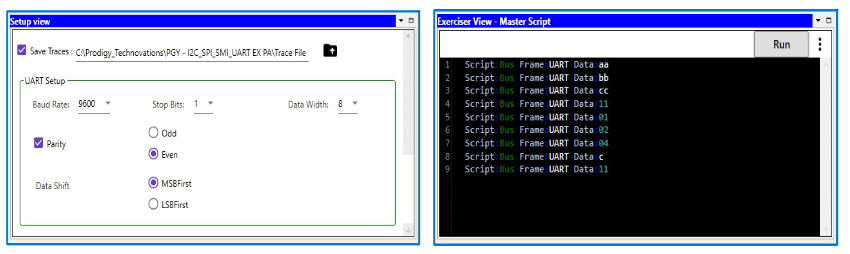

Exerciser

Timing Diagram and Protocol Listing View

The timing view provides the plot of TX signals with a bus diagram. Overlaying of Protocol bits on the digital timing waveform will help easy debugging of Protocol decoded data. Cursor and Zoom features will make it convenient to analyze Protocol in the timing diagram for any timing errors.

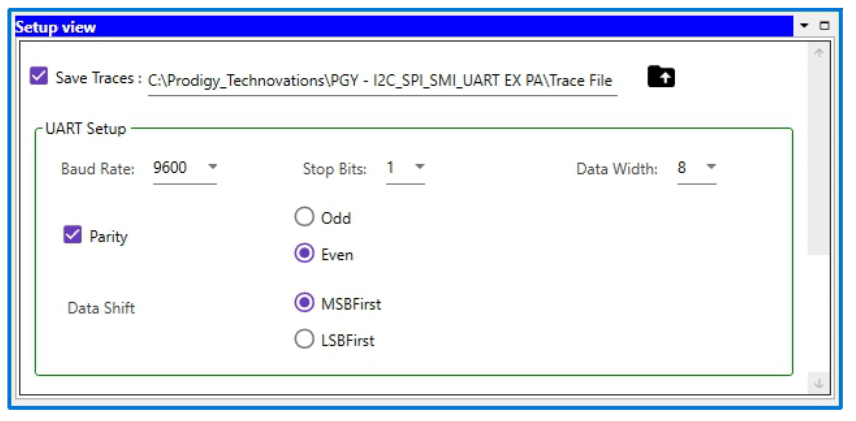

Setup View

Users can configure the PGY-UART-EX-PD for different baud rates, for different configurations of Data width and Stop bits. Users can also choose whether the parity is odd or even depending on the data type being used and also select the data shift type.

Warranty

Hardware and software are covered by a one-year warranty. Probes are covered three months warranty for all manufacturing defects