Description

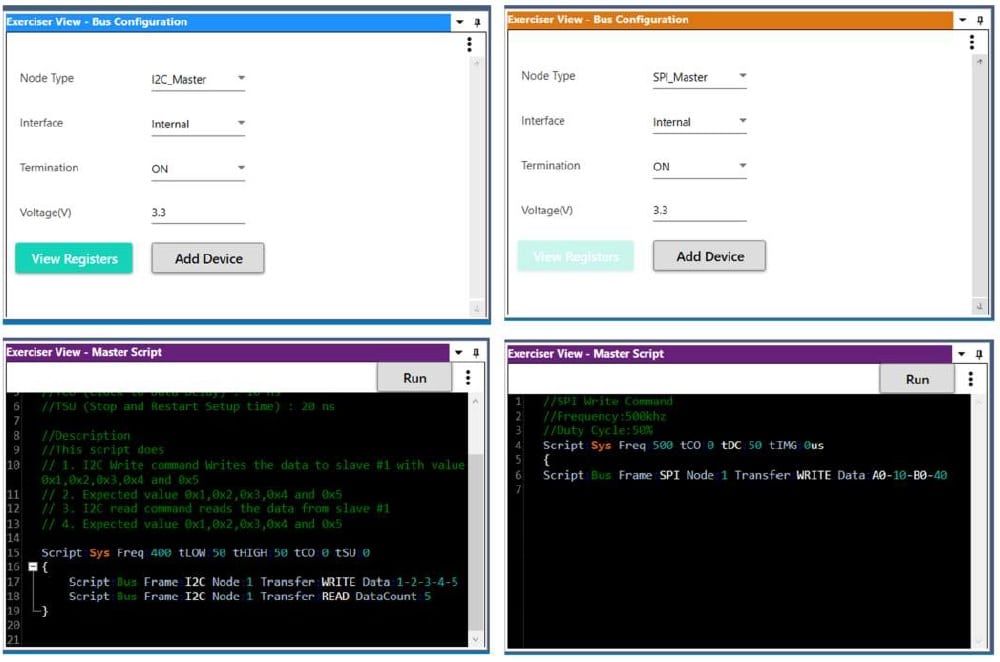

Die Software zur elektrischen Validierung und Protokolldekodierung von SPI bietet elektrische Messungen zur Prüfung der Konformität und Protokolldekodierung gemäß der SPI-Spezifikation. Die PGY-SPI-Software zur elektrischen Validierung und Protokolldekodierung läuft auf den Tektronix Oszilloskopen DPO5000, TDS7000, DPO / DSA / MSO7000 und bietet elektrische Messungen und Protokolldekodierung mit nur einem Mausklick. Dies ermöglicht eine rasche Überprüfung der SPI-Konformität und Flexibilität bei der Fehlersuche. Darüber hinaus können sie den Command und die Response von SPI dekodieren, um die Kommunikation zu debuggen. PGY-SPI nutzt die Vorteile der digitalen Kanäle von MSO und ermöglicht die Dekodierung von SPI-Datenleitungen.

Features SPI Protokoll Software

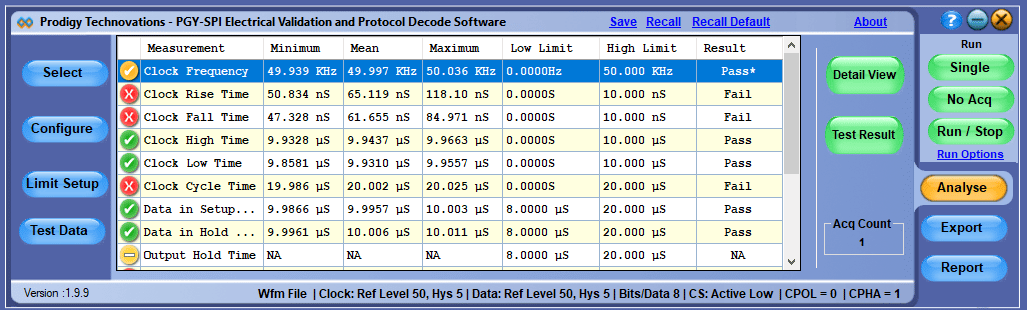

- Automatisierte elektrische Messungen mit einem anpassbaren Referenzpegel des elektrischen SPI-Signals.

- Automatisierte Messungen unabhängig von der Geschwindigkeit des SPI-Busses

- Anpassbare Messgrenzwerteinstellung zur Pass/Fail-Validierung des elektrischen Signals, um Messungen bei unterschiedlichen Datengeschwindigkeiten zu ermöglichen.

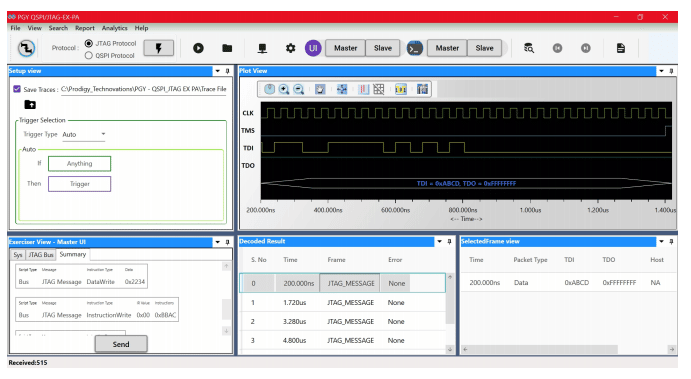

- Dekodierung der SPI-Signale MOSI und MISO zum einfachen Verständnis des Protokolls

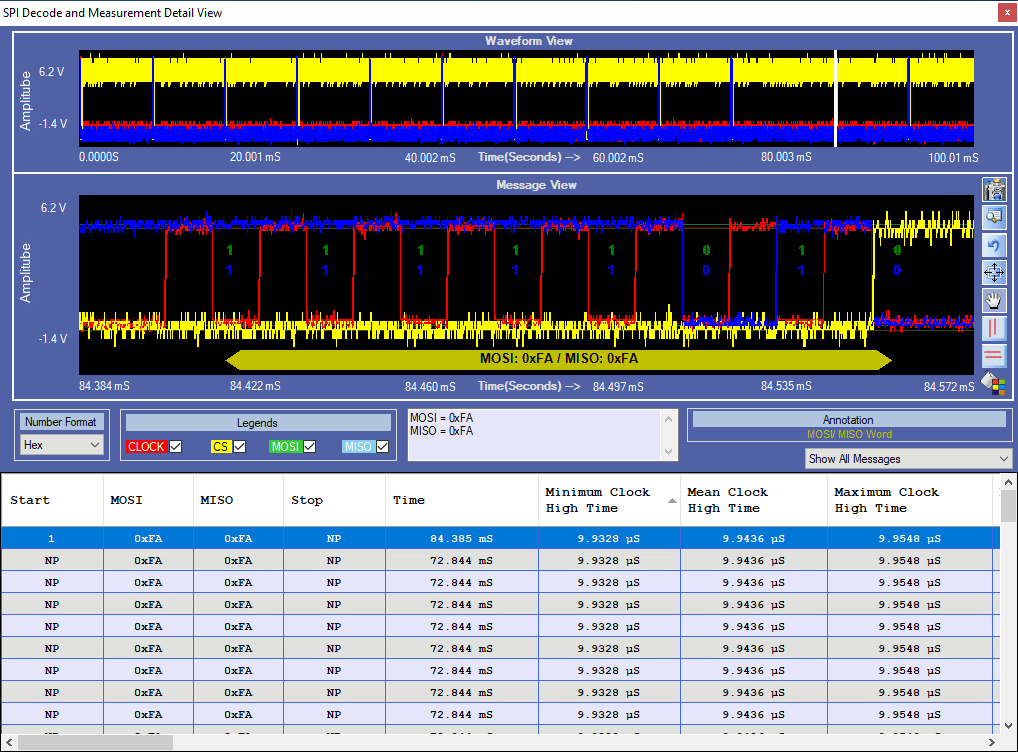

- Verknüpft den Protokollinhalt mit dem elektrischen Signal im Oszilloskop zum einfachen Erfassen der elektrischen Eigenschaften des Protokolls

- Überlagert die Protokolldaten auf der analogen Wellenform in einem Wellenform-Darstellungsfenster

- Vergrößert den Inhalt des ausgewählten SPI-Pakets in der Dekodierungstabelle im Waveform-Plot-Fenster zur einfachen Analyse der elektrischen Eigenschaften des SPI-Frames

- Anzeige von Protokoll- und Dekodierdaten in den Formaten Hexadezimal, Dezimal, Binär, Oktal und ASCII

- Möglichkeit, die SPI-Protokolldaten im CSV- und txt-Format zu speichern

- Utility-Funktionen wie Zoom, Rückgängig machen und Anpassen des Bildschirms für einfaches Debugging, während die Protokolldaten mit der Wellenform korreliert werden

- Erstellung von Berichten im HTML-Format

- Unterstützt WFM- und isf-Dateiformate für die Offline-Analyse

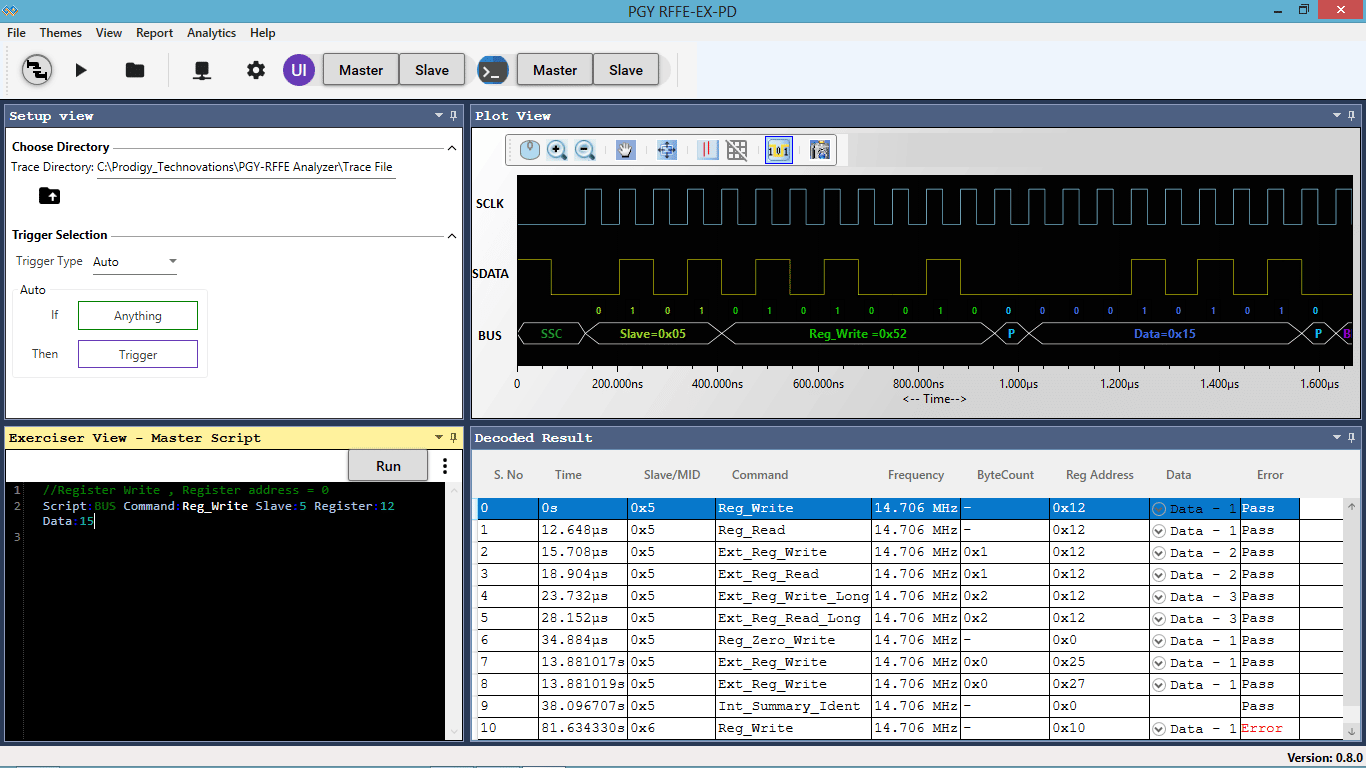

Detailansicht der SPI Dekodierung und Messung im Oszilloskop

Die PGY-SPI Software für elektrische Messungen und Protokolldekodierung bietet elektrische Messungen und Protokolldekodierung für SPI-Busse. Diese Software bietet die Flexibilität, Referenzpegel für elektrische Messungen und benutzerdefinierte Grenzwerte festzulegen, was sie zur vielseitigsten Lösung macht, um verschiedene Anforderungen an die Charakterisierung von SPI-Signalen zu erfüllen. Entwicklungs- und Testingenieure können jetzt automatisch genaue und zuverlässige elektrische Messungen durchführen und Protokolle in der PGY-SPI-Software dekodieren, indem sie Daten verwenden, die mit den Oszilloskopen der Serien DPO5000, TDS7000, DPO/DSA/MSO7000 von Tektronix erfasst wurden, um den Entwicklungs- und Testzyklus zu verkürzen.

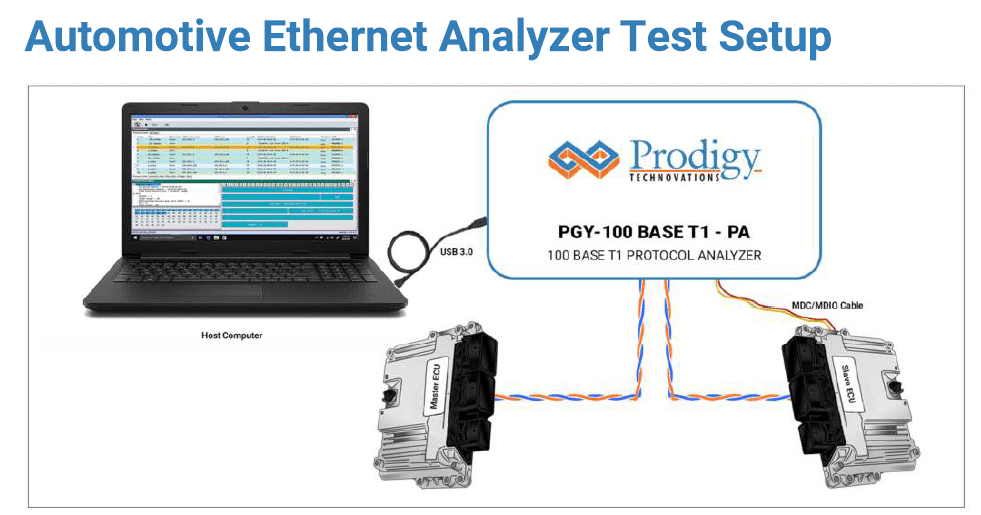

Nahtlose Integration mit Tektronix-Oszilloskopen

Die PGY-SPI-Software läuft innerhalb der Tektronix-Oszilloskope und führt die elektrischen Messungen durch, dekodiert die Protokolle und zeigt die dekodierten Daten in einer Tabelle an und verknüpft die dekodierten Daten mit dem elektrischen Signal in der Wellenformdarstellung. Der auf dem SPI-Protokoll basierende Trigger kann mit den integrierten SPI-Trigger-Funktionen der Tektronix-Oszilloskope eingerichtet werden.

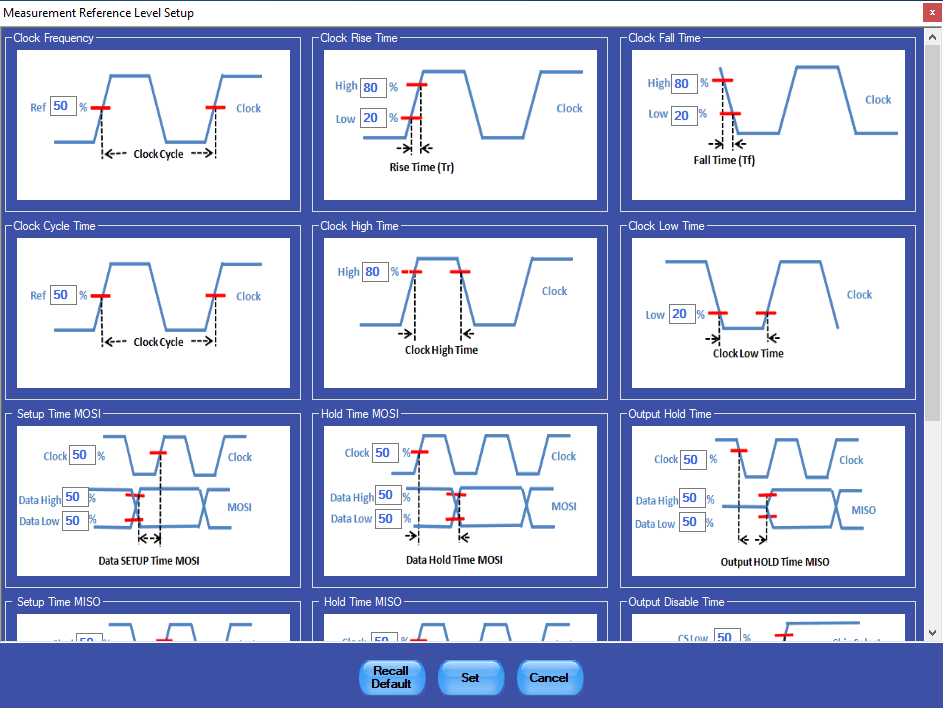

Referenz Level Setup

Für den SPI-Bus sind keine Standardmessgrenzen für Pass/Fail-Tests definiert. Die Grenzwerte variieren in Abhängigkeit von der SPI-Bus-Geschwindigkeit. Zur Charakterisierung und Validierung von SPI-Signalen bietet die PGYSPI-Software ein grafisches Messreferenzpegel-Setup zur Einstellung des Messreferenzpegels von SPI-Signalen. Diese Grenzwerte werden bei der Durchführung ausgewählter SPI-Messungen in der PGY-SPI-Software automatisch angewendet und verkürzen die Testzeit, indem sie zuverlässige Messungen ermöglichen.

Unterstützte Tektronix Oszilloskope

- DPO 5000

- DPO 7000

- MSO 7000

- DSA 7000

- MSO5

- MSO6

Technical Data

| Eigenschaften |  PGY-SPI Software |

|---|---|

| Elektrische Messungen |

|

| Busgeschwindigkeit | Benutzerdefiniert; begrenzt durch Oszilloskop-Bandbreite |

| Protokolldekodierung | Hexadezimal, Oktal, Binär, Dezimal, ASCII |

| Wellenformfenster | Überlagerung der Protokolldekodierungsdaten auf der Wellenform |

| Berichtserstellung | Anpassbarer Bericht im HTML-Format |

| Generierung von Berichten | Anpassbarer Bericht im HTML-Format |

| Export der Daten | CSV- und TXT-Format |