Description

With the industry's first oscilloscope-based PGY-HDMI-PA protocol analyzer software, you can see every event in the MHL/HDMI stream from the MHL/HDMI frame to the physical layer analog signals that traditional protocol analyzers cannot. PGY-HDMI-PA Protocol Analyzer software performs MHL/HDMI protocol conformance testing according to MHL CTS 1.1 and HDMI CTS 1.4a. It provides unmatched flexibility in analyzing, debugging, and correlating test results from MHL/HDMI frame to physical layer analog waveforms to address MHL/HDMI design challenges. For efficient troubleshooting, the PGY-HDMI-PA software provides a unique multi-viewer that includes a frame summary viewer, a frame viewer, a bus viewer, a protocol viewer, a data island viewer, and an event and test result viewer. The automatic linking between all these views allows you to see and correlate the data in different parts of the MHL/HDMI protocol stack. The PGY-HDMI-PA protocol analysis software, along with Tektronix physical layer conformance test solutions and the industry-leading Tektronix high-performance oscilloscope, provides a single-box solution for physical and protocol layer testing.

Features HDMI Protocol Software

- MHL/HDMI Protocol analysis software offers in-depth visibility from the physical layer to video frames with unmatched data correlation between all the layers of MHL/HDMI protocol.

- Transforms the general-purpose oscilloscope into a sophisticated MHL/HDMI Protocol Analyzer.

- Debugging and troubleshooting are made easy by cross-correlating the MHL/HDMI protocol data using a frame summary viewer, frame viewer, Bus viewer, data packet, and event viewer.

- Frame summary view helps to locate error frames for detailed analysis quickly.

- The Frame Viewer helps to view the transmitted frame with color-coded MHL/HDMI operating modes as per the specification and eliminates the need for a Sink device in MHL/HDMI test setup by reproducing the transmitted image in an Oscilloscope display.

- Bus viewer with the Physical layer analog waveforms offers unmatched flexibility in correlating protocol errors with the physical layer.

- The Protocol Viewer displays the tabular view of protocol information with decoded values.

- The Event Viewer lists detailed protocol errors and events in the MHL/HDMI compliance tests to quickly locate the protocol failures.

- Raw and detailed packet information in the Data packet viewer helps to identify the problems in Data Island periods.

- Supports 24, 30, 36, and 48 bits per video pixel for HDMI and 24 bits per pixel for MHL.

- The oscilloscope setup assistant automatically sets up the oscilloscope to obtain accurate and reliable test results.

- Performs the protocol Tests per the MHL Compliance Test specification 1.1 and HDMI Compliance Test specification 1.4a and displays quick Pass/Fail results.

- Conforms to HDMI Specification 1.4a and MHL Specification 1.1.

- Supports Oscilloscope live channels, Tektronix .wfm waveform files, and .bin (P/A/V file format of HDMI Capture card) files Generates comprehensive and customizable reports.

- Ability to export the analyzed data to .bmp, txt, CSV, .bin (P/A/V File format) for advanced analysis.

In-depth MHL/HDMI protocol analysis

For efficient MHL/HDMI protocol debugging and optimization, the PGY-HDMI-PA protocol analysis software has a frame summary viewer, frame viewer, bus viewer, protocol viewer, data packet viewer, and event and test result viewers.

The Frame Summary Viewer shows a thumbnail image for each frame with a summary of the pass/fail test results of the corresponding frame. The view allows you to quickly navigate to the failed frames for detailed analysis.

The Frame Viewer displays the transmitted full image according to the MHL/HDMI specification. For easy identification of the operation modes, the control period, preamble video, preamble data, data protection band, data island and video protection band, and active video are displayed in different colors. Hovering the mouse over the image gives the type of each mode, relative pixel information, the transmitted 10-bit data value, and the corresponding decoded information for that mode. The image viewer eliminates the need for an MHL/HDMI sync device to display the image transmitted from the source.

Frame View

The Frame Viewer displays the transmitted full image according to the MHL/HDMI specification. For easy identification of the operation modes, the control period, preamble video, preamble data, data protection band, data island and video protection band, and active video are displayed in different colors. Hovering the mouse over the image gives the type of each mode, relative pixel information, the transmitted 10-bit data value, and the corresponding decoded information for that mode. The image viewer eliminates the need for an MHL/HDMI sync device to display the image transmitted from the source.

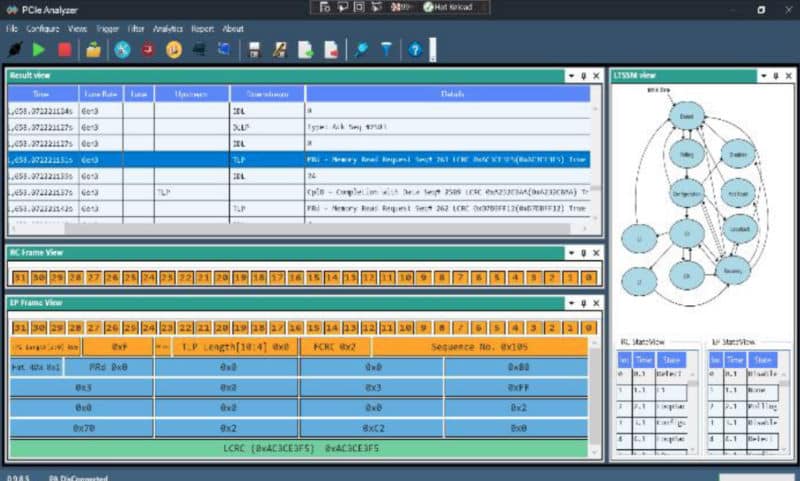

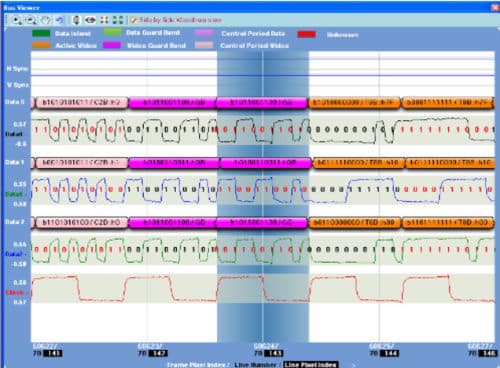

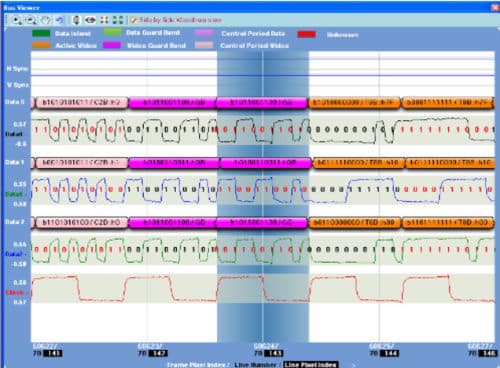

Bus Viewer

The Bus Viewer provides a way to visually review the transmitted MHL/HDMI information in the bus diagram display along with the analog waveforms. The industry's first MHL/HDMI bus diagram and analog waveform with overlapping log data help identify issues related to data skew between pairs and skew between clock and data. Each line is color coded for control period, preamble video, preamble data, data guard band, data island and video guard band, active video for easy error detection. In addition to the bus information, the HDMI bus viewer also provides information about the active periods of H-Sync and V-Sync. The MHL Bus Viewer allows you to view the Data Positive and Data Negative waveforms, as well as the corresponding common mode and data created using the captured MHL signals. The MHL bus diagram also shows the details of the transmitted multiplexed logical channel as well as the demultiplexed logical channels according to the MHL protocol specification. To identify and locate errors in a specific period, the bus viewer provides the pixel index in the selected frame, the line number and the pixel index in the line. Utility functions such as Zoom, Un-Zoom, Pan, Undo, Fit horizontal, Fit vertical, Fit horizontal and vertical and Side-by-Side Waveform and Bus View help to maneuver the bus graph and analyze the MHL/HDMI protocol.

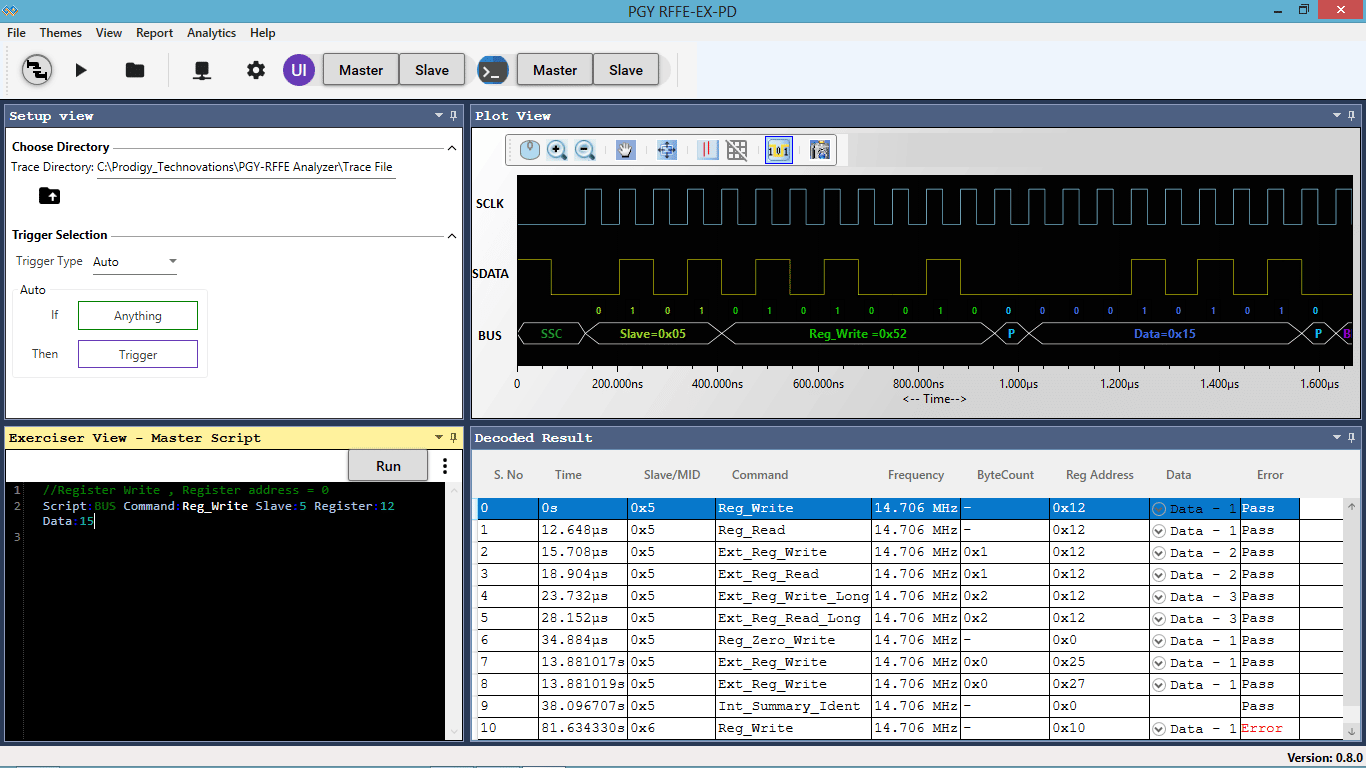

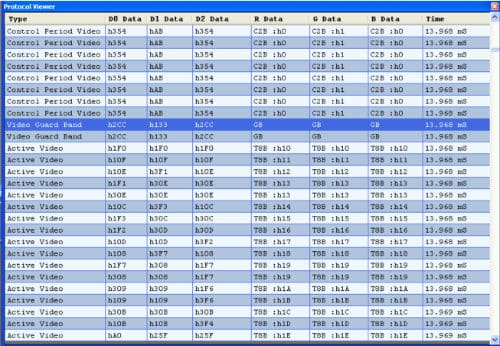

Protocol Viewer

The protocol viewer provides a tabular view of the protocol list with transmitted 10-bit data for each channel along with the decoded 8-bit data for active video, 4-bit TERC4 data for the data island, and 2-bit data for the control period encoding along with the time stamp.

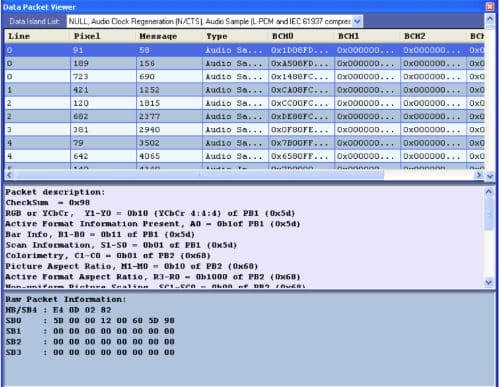

Data Packet Viewer

The data packet viewer lists the entire data packets that were transmitted in the selected frame. Each data island period type, the line number, the pixel number and the BCH data of the data island period are displayed in tabular form. Depending on the packet type, the data packet viewer also provides the details of the data packet according to the CEA 861 specification. The software also performs comprehensive tests according to HDMI conformance test specification 1.4a and MHL conformance test specification 1.1.

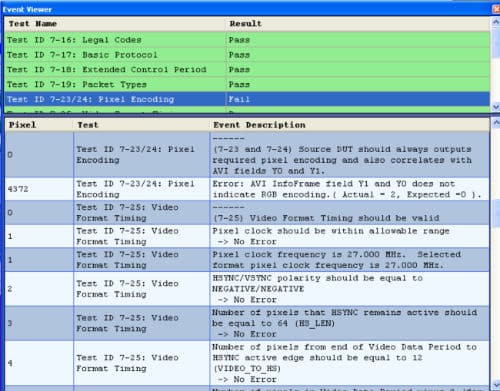

Event and Test results viewer

The event and test result display lists the selected test results together with the description of the individual information on passed and failed tests.

Seamless oscilloscope integration

HDMI Protocol Analysis Software runs inside the Tektronix high-performance Windows Oscilloscope. The Oscilloscope Setup Wizard helps automatically set up the oscilloscope for reliable and accurate test results. It provides the flexibility to capture 2-second video frames according to the MHL/HDMI test procedure or a few frames for quick troubleshooting.

Automatically customizable report and export

The MHL/HDMI software's built-in automatic report generator provides a customizable report creation feature that helps effectively distribute the test report among other team members and management.

Protocol check

The MHL/HDMI software's built-in automatic report generator provides a customizable report generation function that helps communicate test reports effectively between other team members and management. For further data analysis, the software also provides image, log, and data island period data in multiple export formats. The P/A/V binary format helps cross-correlate the PGY-HDMI-PA data using conventional protocol analysis software.

Supported Tektronix Oscilloscopes

- DPO 70000

- MSO 70000

- DSA 70000

.jpg)

.jpg)

.jpg)

.jpg)